- Le signal reset_n permet de réinitialiser le fonctionnement du microprocesseur.

- Au premier coup d’horloge qui suit le passage à 1 du signal reset_n, le microprocesseur va chercher la première instruction du programme, qui se trouve implicitement à l’adresse "0" de la mémoire.

- L’exécution d’une instruction s’effectue systématiquement en trois cycles d’horloge.

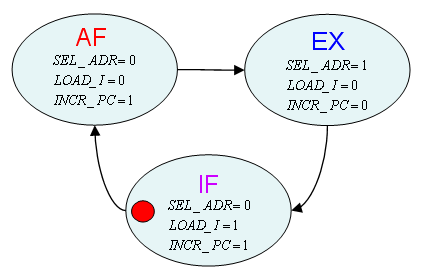

Le graphe de la machine à états est rappelé dans la figure 3 (toutes les sorties ne sont pas indiquées).

Fig. 3 : Graphe d’état du contrôleur CTR

5.1. Premier cycle ''IF''

Pendant le premier cycle (IF pour "instruction fetch") deux opérations sont réalisées simultanément.

- Le registre d’instruction I est chargé (load_I = 1) avec le premier octet de l’instruction. Ce premier octet est lu dans la mémoire à l’adresse donnée par le pointeur PC. A cet effet, PC est positionné sur le bus d’adresse ram_addr de la mémoire (sel_adr = 0).

- La deuxième opération consiste à incrémenter le compteur de programme PC (inc_PC = 1). Cette opération permettra, pour le cycle suivant, de disposer de l’adresse du deuxième octet de l’instruction.

5.2. Deuxième cycle ''AF''

Pendant le deuxième cycle (AF pour "address fetch") deux opérations sont réalisées simultanément.

- Le registre d’adresse AD est chargé (load_AD = 1) avec le deuxième octet de l’instruction. Ce deuxième octet est lu dans la mémoire à l’adresse donnée par le pointeur PC. A cet effet, PC est positionné sur le bus d’adresse ram_addr de la mémoire (sel_adr = 0).

- La deuxième opération consiste à mettre à jour le compteur programme PC. Deux cas peuvent se présenter :

- L’instruction n’est pas un saut. Il faut alors incrémenter le compteur de programme PC (inc_PC=1) de manière à disposer du pointeur du premier octet de l’instruction suivante.

- L’instruction est un saut (instruction JMP, instruction JNZ avec Z=0, ou encore instruction JNC avec C=0). Dans ce cas, le pointeur programme PC reçoit la valeur de la donnée lue en mémoire à l’adresse PC (load_PC = 1).

Remarque : pour simplifier, inc_PC est systématiquement mis à 1. En cas de saut, le bloc PC considérera le signal load_PC comme prioritaire.

5.3. Troisième cycle "EX"

Le troisième cycle correspond à l’exécution proprement dite de l’instruction. L’opération réalisée dépend de l’instruction stockée dans le registre d’instruction I. Dans tous les cas, le contenu de la mémoire à l’adresse déterminée par le pointeur stocké dans AD au cycle précédent, est lu de la mémoire et placé sur le bus d’entrée ram_data (sel_adr = 1).

- Dans le cas d’une instruction "non opératoire" (NOP, STA, OUT, JMP, JNC ou JNZ), le contenu de l’accumulateur n’est pas modifié (LOAD_AZC = 0). Dans le cas contraire, le résultat de l’opération est mémorisé dans l’accumulateur (LOAD_AZC = 1). Remarque : l’instruction LDA est considérée comme une instruction opératoire (accu ⇐ ram_data, donc LOAD_AZC = 1).

- Dans le cas de l’instruction OUT, la valeur du bit de poids faible ram_data[0], est stockée dans le registre BZ (LOAD_BZ = 1).

- Dans le cas de l’instruction STA, le contenu de l’accumulateur accu est stocké en mémoire (ram_write=1) à l’adresse mémoire déterminée par le pointeur stocké dans AD au cycle précédent.

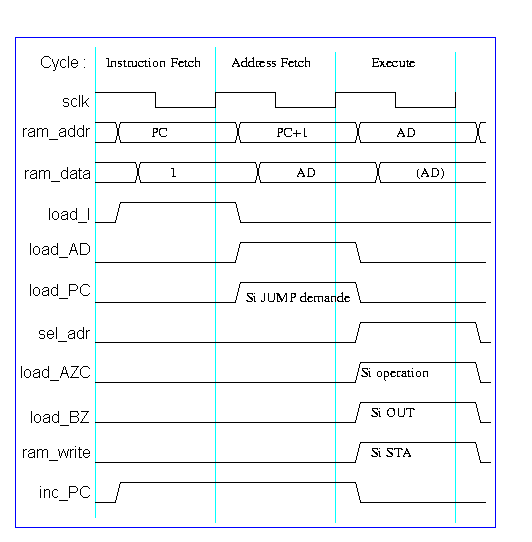

Le chronograme 4 permet de résumer les différents cas.

Fig. 4 : Chronogrammes des cycles du processeur