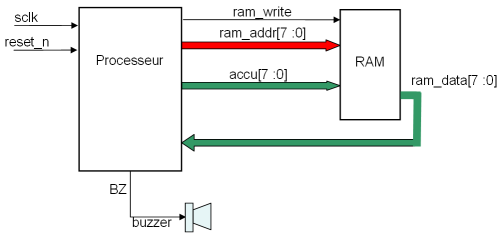

Bien que le sujet du TP concerne davantage le coeur d’exécution du microprocesseur que son environnement d’utilisation, nous présentons ici le système complet implanté sur la maquette de test. Le système proposé se compose :

- du microprocesseur implanté dans un circuit logique programmable Altera Cyclone II EP2C35,

- d'une mémoire RAM contenant le programme et les données (cette mémoire est, elle aussi, intégrée dans le FPGA),

- d’un haut-parleur piloté par un port de sortie du microprocesseur.

Quelques autres périphériques ne sont pas représentés sur le schéma 1:

-

le générateur d’horloge sclk et la génération de la remise à zéro (reset_n),

- les afficheurs pour le debug.

Fig. 1: Schéma global du processeur et de ses périphériques

|

Nom |

Description |

Entrée ou Sortie (vue du processeur) |

|

sclk |

Horloge générale du processeur |

Entrée |

|

reset_n |

Remise à zéro, asynchrone et active au niveau bas |

Entrée |

|

BZ |

Port pouvant être positionné à ’1’ ou ’0’ |

Sortie |

|

ram_addr[7..0] |

Adresse de la RAM |

Sorties |

|

accu[7..0] |

Sortie de l’ACCUmulateur. La valeur de ce bus sera mémorisée dans la RAM à l’adresse ram_addr si ram_write vaut 1 (accès à la RAM en écriture) |

Sorties |

|

ram_data[7..0] |

Données issues de la RAM, à l’adresse ram_addr (accès à la RAM en lecture) |

Entrées |

|

ram_write |

Signal demandant l'écriture à la mémoire |

Sortie |

Tab. 1 : Entrées-sorties du processeur

Remarque : il y a quelques différences par rapport à la leçon sur le nanoprocesseur, portant sur les noms des signaux :

- le bus d’adresse de la RAM est appelé ram_addr[7:0]

- le bus d’entrée de la RAM est appelé directement accu[7:0] (car c’est la sortie de l’accumulateur du processeur)

- le bus de sortie de la RAM est appelé ram_data[7:0]