Nous désirons réaliser un bloc vld permettant de décoder les codes définis ci-dessus. Ce bloc est constitué d'une machine à états synchrone de Moore. Les caractéristiques de la transmission et les contraintes de traitement sont les suivantes :

-

Les symboles codés sont envoyés bit à bit par un signal bit_value, en commençant part les poids forts, de manière synchrone avec une horloge clk.

-

L'émetteur de symboles VLC signale au récepteur la présence d'un bit de symbole à transmettre par l'intermédiaire d'un signal bit_valid.

- L'émetteur de symboles VLC peut enchaîner les symboles sans interruption (pas de cycle d'attente).

-

L'émetteur de symboles peut interrompre temporairement la transmission (bit_valid=0) :

- entre les symboles, mais aussi

- au milieu de la transmission d'un symbole.

- Les symboles seront toujours intégralement transmis (l'émetteur ne fait pas d'erreurs).

-

Le décodeur génère un code data_value de 3bits correspondant au symbole décodé.

- Le signal data_value doit sortir exactement 1 cycle après l'arrivée du dernier bit du code VLC transmis.

-

Le décodeur signale la présence d'un symbole décodé par l'intermédiaire d'un signal data_valid qui ne doit rester à "1" que pendant 1 cycle de clk.

-

Le décodeur peut être initialisé par l'intermédiaire d'un signal reset_n asynchrone actif à l'état bas.

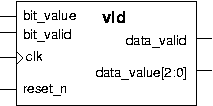

Les figures et tableaux suivants résument les interfaces du bloc VLD:

|

Nom |

Type |

Utilisation |

|

reset_n |

Entrée |

Initialisation de la machine à état, actif à l'état bas |

|

clk |

Entrée |

Horloge |

|

bit_value |

Entrée |

Bits de code qui entrent |

|

bit_valid |

Entrée |

Indique que le signal "bit_value" est valide |

|

data_value |

Sorties |

symbole décodé, recodé comme un entier sur 3 bits |

|

data_valid |

Sortie |

ne dure qu'un cycle, et indique que les sorties "data_value" portent un symbole décodé |

|

error |

Sortie |

Inutilisée pour le moment |

Travail à effectuer

-

Dessiner sur papier le schéma électrique de la machine à états, en séparant bien le registre qui mémorise l'état et les parties combinatoires, et en localisant où se connectent les entrées et les sorties,

-

Dessiner des chronogrammes de ce qui peut se passer dans différents cas, suivant les différentes valeurs possibles prises par les entrées,

-

Dessiner un graphe d'états de la machine à états vld, en précisant tous les états et toutes les transitions en fonction des valeurs des entrées,

-

Donner un nom court et clair à chaque état, indiquer la valeur des sorties data_valid et data_value pour chaque état, préciser l'état initial (celui du reset),

-

On nommera l'état courant EC et l'état futur EF, on définira la table de vérité de EF en fonction de EC et des entrées bit_valid et bit_value. On ne cherchera pas à donner une valeur binaire aux états (la compilation le fera automatiquement), la table de vérité contiendra directement les mnémoniques des états.

Exemple de début de table de vérité :

|

EC |

bit_valid |

bit_value |

EF |

|

DEBUT |

0 |

1 |

A1 |

|

A1 |

1 |

1 |

E2 |

|

... |

... |

... |

... |

- Déterminez le nombre minimum de bits nécessaires au codage des états.

-

Définir de même la table de vérité des sorties data_valid et data_value en fonction de EC :

|

EC |

data_valid |

data_value |

|

A1 |

1 |

1 |

|

E2 |

1 |

3 |

|

... |

... |

... |

-

Prenez la peine de lire la partie concernant le codage des machines à état en SystemVerilog, qui vous permettra :

- de déclarer les états de votre machine à états,

- de traduire très simplement vos tables de vérité.

-

Coder la machine à états en langage System Verilog. Pour cela, complétez le fichier vld.sv situé dans le sous-répertoire src (il est normalement déjà ouvert dans un onglet de l'éditeur eVim). Comme indiqué dans les commentaires du fichier, vous devez explicitement écrire 4 séquences de code :

- Le code qui déclare les noms des états pour les bus EC et EF,

- Le code séquentiel du registre qui mémorise l'état courant EC,

- Le code combinatoire du calcul de l'état futur EF,

- Le code combinatoire du calcul des sorties en fonction de EC.

-

Testez votre code en lançant la commande make simu_vld.

- Vérifiez vous-même le bon fonctionnement de votre décodeur et appelez votre encadrant pour qu'il constate le résultat.