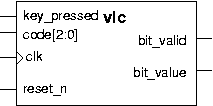

Le bloc vlc est le codeur qui génère les signaux transmis au décodeur que l'on vient de réaliser. Un opérateur humain dispose de 5 boutons numérotés de 1 à 5. Lorsque l'opérateur appuie sur un bouton, cela positionne en entrée de vlc le code du nombre entier de 1 à 5, en parallèle sur 3 fils nommés "code", et cela génère aussi une impulsion longue sur un fil nommé "key_pressed". Le codeur vlc sera réalisé sous forme d'une machine de Moore. Il doit transformer ses signaux d'entrées en signaux respectant le protocole VLC décrit précédemment, avec la donnée en sortie série sur un seul fil "bit_value".

Les figures et tableaux suivants résument les interfaces du bloc VLC :

|

Nom |

Type |

Utilisation |

|

clk |

Entrée |

Horloge |

|

reset_n |

Entrée |

Reset asynchrone, actif à l'état bas |

|

key_pressed |

Entrée |

Indique si une touche est appuyée. Ce signal reste actif au minimum une centaine de cycles |

|

code |

Entrée |

Code sur 3 bits de la touche appuyée. N'est valable que pendant que key_pressed est actif |

|

bit_valid |

Sortie |

indique que le bloc vlc génère sur "bit_value" un bit valide d'un code vlc |

|

vit_value |

Sortie |

valeur du bit de code vlc générée |

Les contraintes sont les suivantes :

-

vlc génère les séquences de bit dès que possible,

-

vlc ne génère qu'une seule séquence de bits lorsqu'une touche est appuyée (pas de répétition des symboles).

Travail à effectuer

-

Réaliser la machine vlc en suivant les mêmes étapes que pour vld, en tentant de minimiser le nombre d'états de la machine: dessin papier des chronogrammes puis du graphe d'état, écriture des tables de vérité des parties combinatoires, codage en langage système vérilog,

-

Éditez-le fichier vlc.sv en suivant les commentaires et le cadre déjà préparé,

-

Simulez votre codeur en exécutant la commande make simu_vlc.

-

-

Le test du couple (vlc,vld) se fait directement sur la maquette (make syn, make program). Vous utiliserez l'analyseur logique pour vérifier la bonne génération des signaux par vlc. Pour cela, les signaux suivants ont été reliés à l'analyseur logique:

clk

code (sur 3 entrées séparées)

key_pressed

bit_value

bit_valid

data_valid

data_value

-

L'analyseur logique sera synchronisé sur un front montant du signal key_pressed, de manière à saisir les enchaînements après l'appui sur un bouton.

-

Le signal key_pressed est relié au bouton KEY 3 de la maquette et le CODE est relié aux switch SW[2:0].

-

La valeur de data_value après passage dans vos codeur et décodeur est affichée sur l'afficheur sept segments HEX0.