L'addition de 2 mots de N bits peut être réalisée à partir de N cellules élémentaires d'addition sur 1bit.

Par analogie, l'ALU sera conçue de façon hiérarchique à partir d'une cellule élémentaire réalisant les opérations demandées sur 1bit. On mettra ensuite 4 exemplaires de cette cellule élémentaire côte à côte afin de réaliser l'ALU de 4 bits.

On commencera donc par la réalisation de la cellule élémentaire sur 1 bit.

4.1. La "cellule" 1 bit

- Le tableau suivant définit l'interface externe de la cellule 1 bit.

|

Nom |

Type |

Utilisation |

|

Ai |

entrée |

Premier opérande de la cellule. (sur 1bit) |

|

Bi |

entrée |

Deuxième opérande de la cellule. (sur 1bit) |

|

CODE[2:0] |

entrée |

Code déterminant l'opération à effectuer (sur 3 bits) |

|

CIN |

entrée |

Retenue entrante, utilisée ou non, suivant l'opération demandée |

|

Si |

sortie |

Résultat sortant de cellule. (sur 1bit) |

|

COUT |

sortie |

Eventuelle retenue sortante dont l'interprétation dépend de l'opération effectuée |

-

En vous aidant du cours sur les fonctions logiques de base et les opérateurs arithmétiques, définissez l'architecture de cette cellule. C'est un travail papier, vous pouvez à votre gré faire un shéma, définir des expressions algébriques ou des tables de vérité.

-

Prenez le temps de lire les deux premières partie de la page décrivant la syntaxe du SystemVerilog.

-

Enfin, décrivez en SystemVerilog la structure de votre cellule, en complétant le fichier cellule.sv qui est déjà ouvert dans la fenêtre de l'éditeur eVim. Respectez scrupuleusement les noms des signaux (majuscules-minuscules) et les indications. Vous écrirez séparément le code pour Si et le code pour COUT.

Nous avons préparé un environnement de vérification de votre cellule:

-

Sauvez votre fichier cellule.sv puis simulez votre cellule. Pour cela, exécutez la commande make sim_cell depuis la fenêtre de terminal déjà ouverte.

Si des erreurs sont signalées, vous devez corriger le fichier de code-source de votre cellule, puis relancer la simulation.

4.2. L'ALU 4bits

L'ALU 4 bits est obtenue en assemblant quatre cellules de base.

- Définissez l'organisation de cette structure

-

Complétez le fichier alu.sv

-

Vérifiez le bon comportement de votre ALU en utilisant la commande make sim_alu

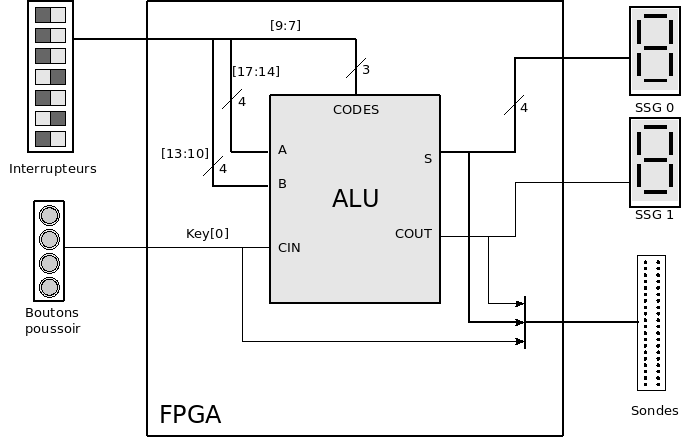

Pour le moment, nous n'avons fait que des simulations, il reste à intégrer réellement votre ALU dans la maquette. La figure suivante décrit l'interface simplifiée entre votre ALU et les éléments de la maquette. Cette interface existe et vous n'avez pas à la réaliser.

-

Executez la commande make syn_alu qui permet de réaliser la synthèse de l'ensemble du projet, et de générer la netlist pour la future programmation du FPGA.

Cette étape prend un certain temps de calcul pour s'exécuter, d'où l'intérêt de corriger les erreurs avant, en faisant des simulations. Le synthétiseur peut détecter des erreurs que la simulation n'a pas mises en évidence. Si tel est le cas, faites vous aider par votre encadrant pour en déterminer l'origine.

-

Avant de passer aux phases suivantes qui utuilisent le FPGA de la maquette ALTERA, vérifiez que la maquette est connectée, alimentée, et mise en marche (LEDs allumées).

-

Envoyez le programme au FPGA de la maquette, grâce à la commande make prg_alu.

Une fois le téléchargement effectué, vous pouvez tester le fonctionnement de votre ALU (électronique cette fois, non simplement simulé), en jouant sur les interrupteurs et les bouton-poussoirs. Le tableau suivant donne la correspondance des entrées/sorties sur la maquette:

|

Signal |

type |

correspondance |

type |

|

A |

entrée |

SW[17:14] |

interrupteurs |

|

B |

entrée |

SW[13:10] |

interrupteurs |

|

CODE |

entrée |

SW[9:7] |

interrupteurs |

|

CIN |

entrée |

Key[0] |

bouton poussoir |

|

S |

sortie |

Hex0 |

Aff. 7 segments |

|

COUT |

sortie |

Hex1 |

Aff. 7 segments |

- Montrez le résultat de votre travail à un encadrant du TP...

4.3 Temps de calcul d'un Additionneur 8bits

- A partir de l'ALU 4bits, déterminez la structure d'une ALU 8 bits

- Complétez le fichier alu_8bits.sv

- Simulez par la commande make sim_8bits.

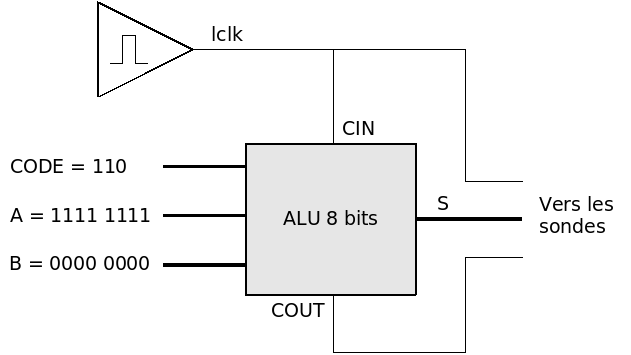

Mesure des temps de propagation en mode addition

Pour mesurer les temps de calcul en mode additionneur de votre ALU 8bits, nous avons préparé une configuration où le code est forcé à la valeur correspondant à l'addition:

-

L'entrée A est forcée à 11111111

-

L'entrée B est forcée à 00000000

-

La retenue entrante CIN a été reliée à un signal d'horloge lclk qui prend à intervale régulier les valeurs 1 et 0.

-

4. Synthétisez l'alu 8 bits par la commande make syn_8bits

-

Programmez le FPGA par la commande make prg_8bits

- Quelle valeur doit prendre la sortie S lorsque Cin vaut 0 ?

- Quelle valeur doit prendre la sortie S lorsque Cin vaut 1 ?

Quand la retenue entrante passe de 0 à 1, le changement de S n'est pas instantané, c'est ce que vous devez observer. Pour cela nous avons connecté les sondes de l'analyseur logique. Les sorties suivantes sont visualisables:

-

lclk

S0 à S7 : les 8 sorties de l'ALU

Cout

- Configurez l'analyseur logique pour qu'il se synchronise sur un front du signal de la sonde correspondant à lclk. (faites vous aider pour cela par un encadrant)

- Observez les signaux, notez le temps de sortie de chacun des bits de S par rapport à l'arrivée de la retenue.

- Expliquez le comportement des sorties.

- Notez de même le temps de calcul total de l'addition.

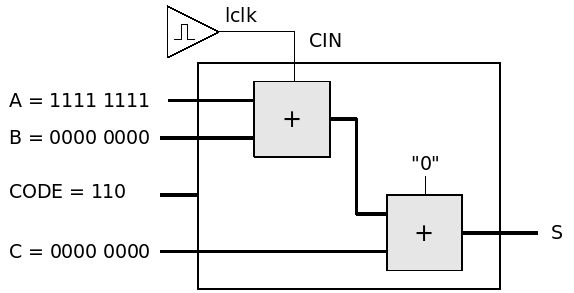

4.4. Addition de 3 mots de 8bits

Nous désirons additionner 3 mots A,B et C codés sur 8bits. Le résultat attendu est codé sur 8 bits.

L'équation attendue est donc : S = A + B + C + Cin

- Déterminez la structure de calcul nécessaire en utilisant 2 instances de l'ALU 8bits du paragraphe 4.3

- Complétez le fichier alu_abc.sv

- Vérifiez votre structure par la commande make sim_abc

- Synthétisez vote alu par la commande make syn_abc

Nous allons déterminer la vitesse de calcul de votre structure en utilisant le shéma suivant:

-

AVANT DE PROGRAMMER votre alu, répondez au mini qcm suivant, et justifiez votre réponse (jouez le jeu SVP...)

- Je pense que le temps de calcul sera proche du temps de calcul de l'ALU 8bits.

- Je pense que le temps de calcul sera proche du double du temps de calcul de l'ALU 8bits

- Je n'ai aucune idée de la relation avec le temps de calcul de l'ALU 8bits

-

Programmez votre FPGA par la commande make prg_abc

- Examinez la sortie des signaux, et remettez éventuellement en cause la réponse précedente.

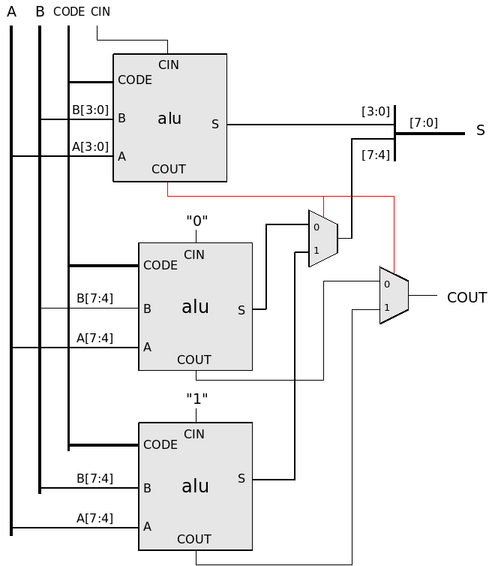

4.5 Un drôle d'additionneur 8 bits

Le shéma suivant représente une variante d'additionneur 8bits utilisant votre ALU 4 bits (celle du paragraphe 4.2)

- Complétez le fichier alu_csa.sv en reproduisant le montage proposé.

- Vérifiez votre ALU par la commande make sim_csa

- Synthétisez : make syn_csa

- Programmez : make prg_csa

- Examinez les sorties, déterminez le temps de calcul de l'addition 8bits et comparez au résultat du paragraphe 4.3

- Expliquez le résultat obtenu, et les avantages et inconvénients d'un tel montage.