2.1. Maquette

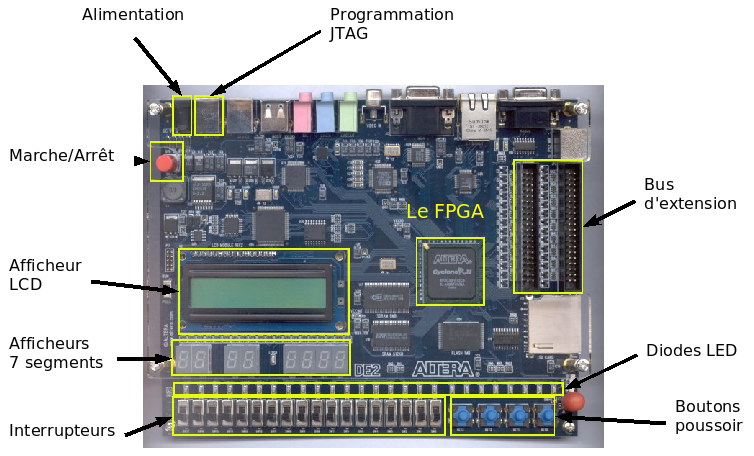

La maquette est construite autour d'un circuit logique programmable de type FPGA. Elle possède un grand nombre d'entrée/sorties toutes connectées au FPGA:

- 18 interrupteurs

- 4 Boutons poussoirs

- 8 afficheurs 7 segments

- 18 diodes LEDS rouges et 9 vertes

- 2 bus d'extension offrants 76 signaux accessibles

- 1 afficheur LCD 2 rangées de 16 caractères

- 1 entrée/sortie clavier/souris et RS232

- 2 ports USB

- 1 sortie moniteur VGA

- 1 entrée vidéo (NTSC/PAL/multi-format)

- Un codec Audio

Une photo de la maquette apparaît ci-dessous. Vous pouvez retrouver le FPGA, les E/S , le connecteur d'alimentation, le connecteur de programmation (via votre PC), ainsi que les connecteurs d'extension. Ces derniers permettront de connecter les sondes d'un analyseur logique de manière à observer les signaux sortants du FPGA.

En annexe, vous trouverez une documentation complète du FPGA et de la maquette.

2.2 Le logiciel de CAO

Les logiciels de CAO électronique aident le concepteur dans toutes les étapes du flot de conception d'un circuit. Les principales étapes pour un FPGA sont :

- La saisie : c'est l'écriture ou "codage" du fonctionnement du circuit et de sa décomposition en composants plus simples. On peut la considérer comme la traduction de la spécification. Elle peut être soit graphique avec des symboles de portes logiques , ou textuelle à l'aide de langages informatiques tels que "System Verilog", "verilog" ou "vhdl". Durant ce TP vous utiliserez le langage "System Verilog".

- La vérification : la vérfication consiste très souvent en une simulation du circuit, c'est à dire l'exécution d'un programme constitué d'un modèle du circuit dont les entrées sont pilotées par des variables évoluant temporellement. Le code saisi dans l'étape précédente sera le modèle utilisé par le "simulateur logique".

- La synthèse : cette étape est chargée de transformer et d'optimiser le modèle saisi en un ensemble de fonctions logiques disponibles dans le composant cible (notre FPGA). Cet ensemble de portes interconnectées s'appelle aussi "liste d'équipotentielles" ou "netlist"

- Le placement/routage : cette étape est chargée d'associer à chaque fonction logique de la netlist une ressource physique du FPGA. L'emplacement de ces ressources étant connu, les connexions entre portes sont transformées en vrais fils conducteurs entre ces ressources.

- La programmation : le fichier décrivant la "netlist" placée et routée est téléchargé dans le FPGA.