# ELECINF 102 : Processeurs et Architectures Numériques

Introduction et logique combinatoire

Laurent Sauvage

[<laurent.sauvage@telecom-paristech.fr>](mailto:laurent.sauvage@telecom-paristech.fr)

# Objectifs du cours

- Comprendre les fonctions de base de l'électronique numérique

- Comprendre la logique combinatoire et synchrone

- Comprendre comment concevoir des opérateurs

- Comprendre comment concevoir un processeur

# Informations utiles

- Site pédagogique : <http://sen.enst.fr/elecinf102>

- Équipe enseignante : Yves Mathieu (responsable du module), Jean-Luc Danger, Tarik Graba, Laurent Sauvage, Guillaume Duc

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

# Le signal électrique

## Support de l'information

- Passer de grandeurs physiques à des signaux électriques grâce à :

- Capteurs

- Transducteurs

- Possibilité de mesurer/manipuler :

- la tension

- le courant

- la charge ...

- C'est pour cela qu'on fait de l'électronique

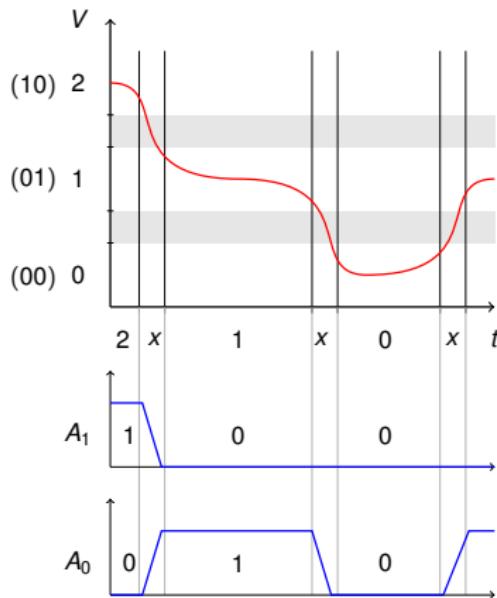

# Codage numérique de l'information

- Discréteriser le signal dans le temps

- échantillonnage

- Représenter le signal par nombre fini de valeurs (de nombres)

- quantification

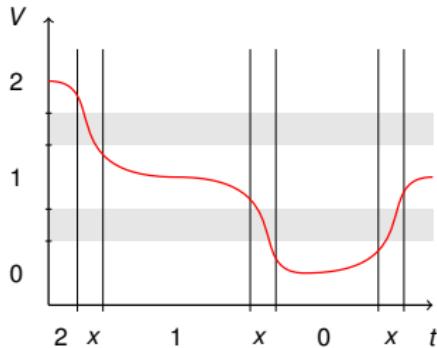

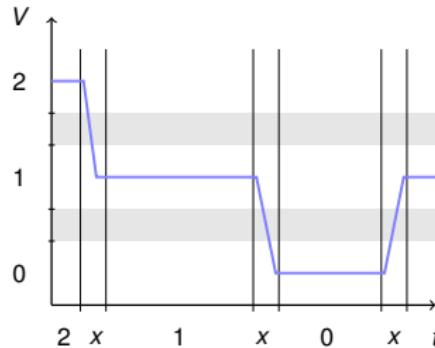

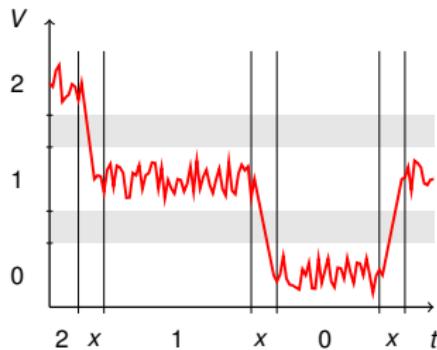

# Codage numérique de l'information

- Discréteriser le signal dans le temps

- échantillonnage

- Représenter le signal par nombre fini de valeurs (de nombres)

- quantification

# Codage numérique de l'information

- Discréteriser le signal dans le temps

- échantillonnage

- Représenter le signal par nombre fini de valeurs (de nombres)

- quantification

# Codage numérique de l'information : intérêts

- Possibilité de reproduire sans perte et de façon illimitée

- Indépendance du support utilisé

- Câble électrique

- Fibre optique

- CDROM, disque dur...

- Possibilité de traiter l'information dans un ordre arbitraire

# Codage binaire

## ■ Interprétations logiques multiples

- 0/1

- vrai/faux

## ■ Support électrique très simple

- Codage utilisant deux valeurs

# Codage binaire : travailler en base 2

Comment représenter plus de deux niveaux en binaire ?

- Utiliser plusieurs fils

- Les transmettre à tour de rôle

Chaque élément est un **bit**

- **binary digit**

On peut représenter tous les nombres en base 2

# Le bit

## ■ Extensions

- 2 niveaux de tension (0/5V ou -12/12V ou ...)

- 2 niveaux de courant électrique

- Absence/présence de lumière sur une fibre

- ...

## ■ Interprétations

- Vrai/Faux pour de la logique et le contrôle

- Ordinateur

- Des nombres pour du calcul

- Calculateur

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

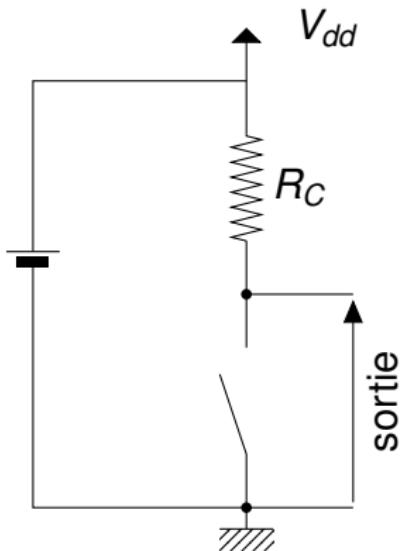

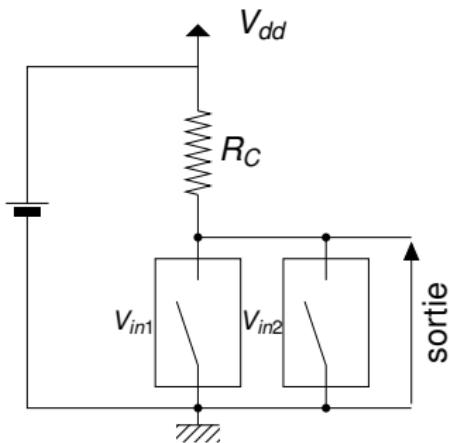

# Génération d'un signal électrique binaire

- Interrupteur fermé

→  $0V$  en sortie

- Interrupteur ouvert

→  $V_{dd}$  en sortie

| tension  | niveau logique |

|----------|----------------|

| $0V$     | 0              |

| $V_{dd}$ | 1              |

# Extraction d'un signal électrique binaire

## ■ Interrupteur commandé :

- Si  $V_{in} < V_{ref}$  alors l'interrupteur est ouvert

- Si  $V_{in} > V_{ref}$  alors l'interrupteur est fermé

## ■ Cet interrupteur peut être :

- Un relais électromagnétique

- Un tube à vide

- Un transistor

# Opérateur de traitement binaire

## Fonction Non

| $V_{in}$    | $V_s$    | $In$ | Sortie |

|-------------|----------|------|--------|

| $< V_{ref}$ | $V_{dd}$ | 0    | 1      |

| $> V_{ref}$ | 0V       | 1    | 0      |

- La fonction Non

- La sortie vaut 0 ssi l'entrée vaut 1

# Opérateur de traitement binaire

## Fonction Non–Ou

| $V_{in1}$   | $V_{in2}$   | $V_s$    | $In_1$ | $In_1$ | Sortie |

|-------------|-------------|----------|--------|--------|--------|

| $< V_{ref}$ | $< V_{ref}$ | $V_{dd}$ | 0      | 0      | 1      |

| $< V_{ref}$ | $> V_{ref}$ | $0V$     | 0      | 1      | 0      |

| $> V_{ref}$ | $< V_{ref}$ | $0V$     | 1      | 0      | 0      |

| $> V_{ref}$ | $> V_{ref}$ | $0V$     | 1      | 1      | 0      |

- Fonction Non–Ou

- la sortie vaut 0 si l'une des entrées vaut 1

# De l'opérateur de traitement binaire au microprocesseur

- Assemblage simples :

- Portes logiques

- Assemblage en opérateurs

- Arithmétique, contrôle ...

- Circuits électroniques exécutant des fonctions complexes

- Microprocesseur

- ASIC<sup>1</sup> (Circuits spécifiques à une application)

- Circuits logiques programmables

---

## 1. Application Specific Integrated Circuit

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

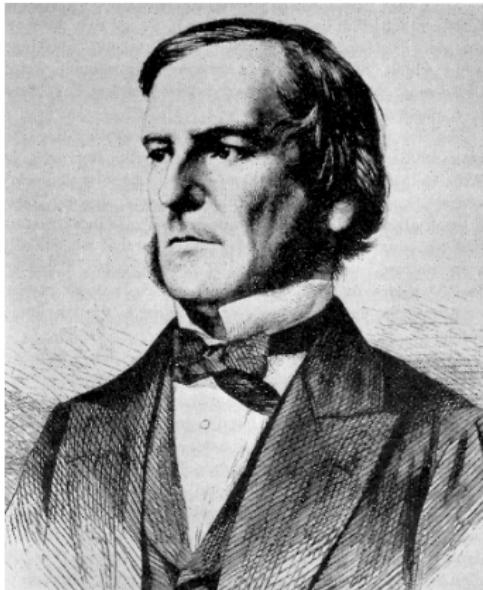

# Algèbre de Boole

## Formalisme de la logique

On le doit à George Boole

Crédits image : wikipedia ([http://fr.wikipedia.org/wiki/George\\_Boole](http://fr.wikipedia.org/wiki/George_Boole))

# Variables et fonctions logiques

## Variables logiques

- Une variable logique est un élément qui appartient à l'ensemble  $E = \{0, 1\}$

- Ne possède que deux états possibles : 0 ou 1

## Fonctions logiques

- Fonction d'une ou plusieurs variables logiques.

$$\left\{ \begin{array}{l} E \times E \dots \times E \rightarrow E \\ e_0, e_1, \dots, e_n \rightarrow s = F(e_0, e_1, \dots, e_n) \end{array} \right.$$

# Fonctions logiques

Deux catégories

## Fonctions combinatoires

La sortie ne dépend que de l'état actuel des entrées

$$\forall t, s(t) = F(e_0(t), e_1(t), \dots, e_n(t))$$

## Fonctions séquentielles

La sortie dépend de l'état actuel des entrées et de leur passé

$$s(t) = F(e_0(t), e_1(t), \dots, e_n(t), e_0(t - t_1), e_1(t - t_1) \dots)$$

# Fonctions logiques

## Représentations

Plusieurs représentations possibles :

**Table de vérité** : En donnant toutes les valeurs possibles pour toutes les entrées possibles.

**Analytique** : En donnant l'équation analytique

**Graphique** : En utilisant les symboles de fonctions de base

**HDL** : Langage “informatique” de description du matériel

(Hardware Description Language)

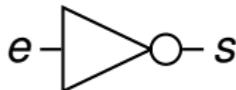

# Fonctions élémentaires

## L'inverseur (Not)

- La sortie est le complément de l'entrée

- La sortie vaut 1 si et seulement si l'entrée vaut 0

**Symbole**

**Équation**

$$s = \bar{e}$$

**Table de vérité**

| $e$ | $s$ |

|-----|-----|

| 0   | 1   |

| 1   | 0   |

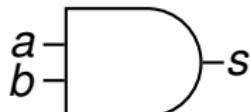

# Fonctions élémentaires

## Le “et” (And)

- La sortie vaut 1 si et seulement si les deux entrées valent 1

- Si l'une des entrées vaut 0 alors la sortie vaut 0

**Symbol**

**Équation**

$$s = a \cdot b$$

**Table de vérité**

| a | b | s |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

# Fonctions élémentaires

## Le “ou” (Or)

- Si l'une des entrées vaut 1 alors la sortie vaut 1

- La sortie vaut 0 si et seulement si les deux entrées valent 0

**Symbol**

**Équation**

$$s = a + b$$

**Table de vérité**

| $a$ | $b$ | $s$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 1   |

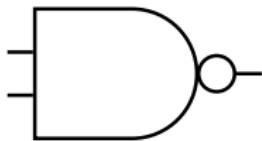

# Fonctions de base

## Le “non et” (Nand)

- La fonction complémentaire du And

- La sortie vaut 1 si l'une des entrées est à 0

**Symbole**

**Équation**

$$s = \overline{a \cdot b}$$

**Table de vérité**

| a | b | s |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

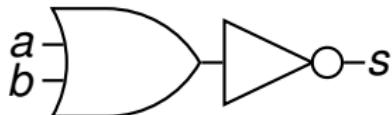

# Fonctions de base

## Le “non et” (Nand)

- La fonction complémentaire du And

- La sortie vaut 1 si l'une des entrées est à 0

| Symbole                                                                           | Équation                   | Table de vérité                                                                                                                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | $s = \overline{a \cdot b}$ | <table border="1"><thead><tr><th>a</th><th>b</th><th>s</th></tr></thead><tbody><tr><td>0</td><td>0</td><td>1</td></tr><tr><td>0</td><td>1</td><td>1</td></tr><tr><td>1</td><td>0</td><td>1</td></tr><tr><td>1</td><td>1</td><td>0</td></tr></tbody></table> | a | b | s | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| a                                                                                 | b                          | s                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                 | 0                          | 1                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                 | 1                          | 1                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                 | 0                          | 1                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                 | 1                          | 0                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

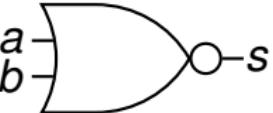

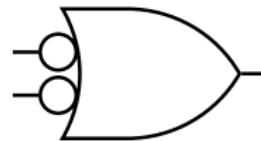

# Fonctions de base

## Le “non ou” (Nor)

- La fonction complémentaire du Or

- La sortie vaut 0 si l'une des entrées est à 1

**Symbole**

**Équation**

$$s = \overline{a + b}$$

**Table de vérité**

| a | b | s |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

# Fonctions de base

## Le “non ou” (Nor)

- La fonction complémentaire du Or

- La sortie vaut 0 si l'une des entrées est à 1

| Symbole                                                                           | Équation               | Table de vérité                                                                                                                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|  | $s = \overline{a + b}$ | <table border="1"><thead><tr><th>a</th><th>b</th><th>s</th></tr></thead><tbody><tr><td>0</td><td>0</td><td>1</td></tr><tr><td>0</td><td>1</td><td>0</td></tr><tr><td>1</td><td>0</td><td>0</td></tr><tr><td>1</td><td>1</td><td>0</td></tr></tbody></table> | a | b | s | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| a                                                                                 | b                      | s                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                 | 0                      | 1                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                 | 1                      | 0                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                 | 0                      | 0                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                 | 1                      | 0                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

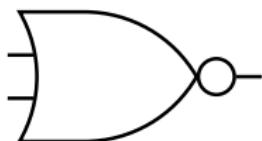

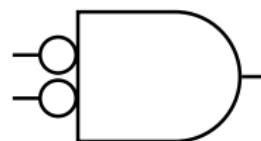

# Équivalence And/Or

Théorème de De Morgan

$$\overline{a + b} = \overline{a} \cdot \overline{b}$$

$\equiv$

$$\overline{a \cdot b} = \overline{a} + \overline{b}$$

$\equiv$

# Exercice

- Comment réaliser une porte à deux entrées, dont la sortie vaut '1' si et seulement si les deux entrées sont différentes ?

- Comment réaliser une porte à deux entrées, dont la sortie vaut '1' si et seulement si les deux entrées sont identiques ?

# Fonctions de base

## Le “Ou exclusif” (Xor)

- La sortie vaut 1 si une seule entrée est à 1

- La sortie vaut 1 si les deux entrées sont différentes

**Symbol**

**Équation**

$$s = a \oplus b$$

$$s = a \cdot \bar{b} + \bar{a} \cdot b$$

**Table de vérité**

| a | b | s |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

# Fonctions de base

## Le “Non Ou exclusif” (Xnor)

- La sortie vaut 1 si les deux entrées sont identiques

- C'est la fonction complémentaire du xor

- C'est la porte égalité

Symbole

Équation

$$s = \overline{a \oplus b}$$

$$s = a \cdot b + \bar{a} \cdot \bar{b}$$

Table de vérité

| a | b | s |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

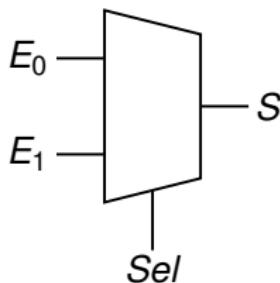

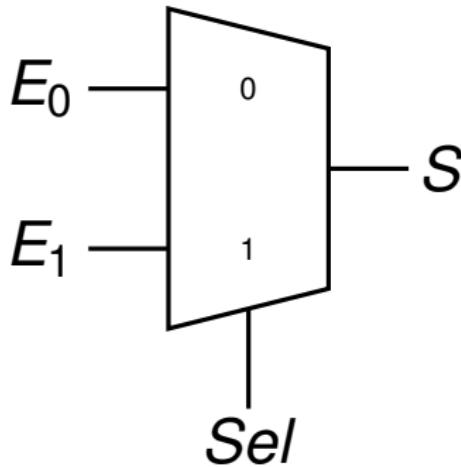

# Exercices ?

## Multiplexeur

- On veut réaliser une fonction d'aiguillage  $2 \rightarrow 1$ .

- Cette porte permet de sélectionner l'une des deux entrées en fonction d'une troisième entrée de sélection

# Le multiplexeur

## La fonction d'aiguillage

| <i>Sel</i> | $E_1$ | $E_0$ | $S$ |

|------------|-------|-------|-----|

| 0          | 0     | 0     | 0   |

| 0          | 0     | 1     | 1   |

| 0          | 1     | 0     | 0   |

| 0          | 1     | 1     | 1   |

| 1          | 0     | 0     | 0   |

| 1          | 0     | 1     | 0   |

| 1          | 1     | 0     | 1   |

| 1          | 1     | 1     | 1   |

$$S = Sel \cdot E_1 + \overline{Sel} \cdot E_0$$

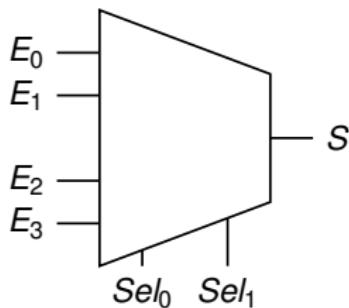

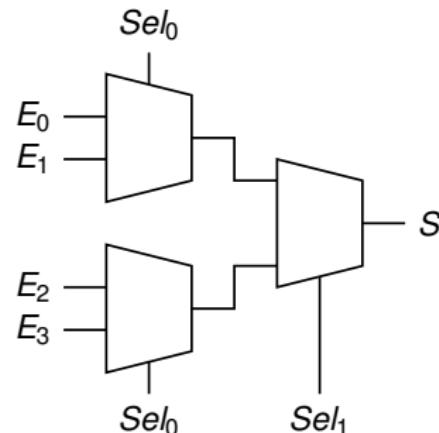

# Le multiplexeur

Fonction d'aiguillage à quatre entrées

4 entrées  $\Rightarrow$  2 entrées de sélection

Peut être réalisé à partir de 3 mux 2 vers 1

$$S = \overline{Sel_1} \cdot \overline{Sel_0} \cdot E_0 + \overline{Sel_1} \cdot Sel_0 \cdot E_1 + Sel_1 \cdot \overline{Sel_0} \cdot E_2 + Sel_0 \cdot Sel_1 \cdot E_3;$$

# Le multiplexeur

## Généralisation

Pour un multiplexeur à  $n$  entrées ( $n = 2^p$  une puissance de 2) :

- Il faut  $p = \log_2(n)$  entrées de sélection

- Il peut être réalisé avec  $n - 1$  multiplexeurs à 2 entrées organisés en  $p$  couches

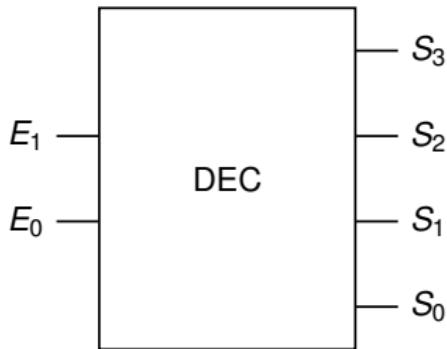

# Le décodeur

- $n$  entrées  $2^n$  sorties.

- Une seule sortie à 1, toutes les autres à 0.

| $E_0$ | $E_1$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     |

- La valeur de l'entrée  $E$  représente l'indice de la sortie active.

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

# Représentation des nombres

## Les nombres naturels

Un entier positif  $N$  dans une base  $b$  se représente par un vecteur  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$  tel que :

$$N = a_{n-1} \cdot b^{n-1} + a_{n-2} \cdot b^{n-2} + \dots + a_1 \cdot b^1 + a_0 \cdot b^0$$

Où :

- $a_{n-1}$  est le chiffre le plus significatif

- $a_0$  est le chiffre le moins significatif

- $a_i$  appartient à un ensemble de  $b$  symboles valant de 0 à  $b - 1$

# Bases souvent utilisées

## ■ $b = 10$

- Représentation Décimale

- $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$

## ■ $b = 16$

- Représentation Hexadécimale

- $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F\}$

## ■ $b = 8$

- Représentation Octale

- $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7\}$

## ■ $b = 2$

- Représentation Binaire

- $a_i \in \{0, 1\}$  est un bit (binary digit)

# Représentation binaire

## Les nombres naturels

Un entier positif  $N$  en base 2 se représente par un vecteur  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$  tel que :

$$N = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \dots + a_1 \cdot 2^1 + a_0 \cdot 2^0$$

Où :

- $a_i$  est un bit appartenant à un ensemble de 2 symboles valant 0 ou 1

- $a_{n-1}$  est le bit le plus significatif (*Most Significant Bit – MSB*)

- $a_0$  est le bit le moins significatif (*Least Significant Bit – LSB*)

# Exemples

- Représentez 2, 3, 4 en binaire

- Représentez 54 en binaire

# Binaire $\leftrightarrow$ Hexadécimal

Hexadécimal = base 16

$$N = \sum_{i=0}^{n-1} a_i \cdot 2^i$$

Profitons du fait que  $2^4 = 16$ . Pour simplifier l'expression le nombre de bit n est supposé être multiple de 4

$$N = \sum_{k=0}^{n/4-1} (a_{4k+3} \cdot 8 + a_{4k+2} \cdot 4 + a_{4k+1} \cdot 2 + a_{4k}) \cdot 16^k$$

Passer à une représentation hexadécimale permet d'avoir une représentation compacte !

# Exemples

- Représentez 54 en hexadécimal

- Représentez 254 en hexadécimal

- En déduire la représentation en binaire

# Exemples

■ Représentez 13 et 29 en binaire :

- en utilisant 4 bits

- en utilisant 5 bits

# Représentation binaire

## Taille finie

Physiquement, le nombre de bits ne peut être infini !

- Il y a  $2^n$  valeurs représentables

- En utilisant  $n$  bits on ne peut représenter que les nombres dans l'intervalle  $[0, 2^n - 1]$ .

- L'arithmétique sur ces représentations est faite modulo  $2^n$

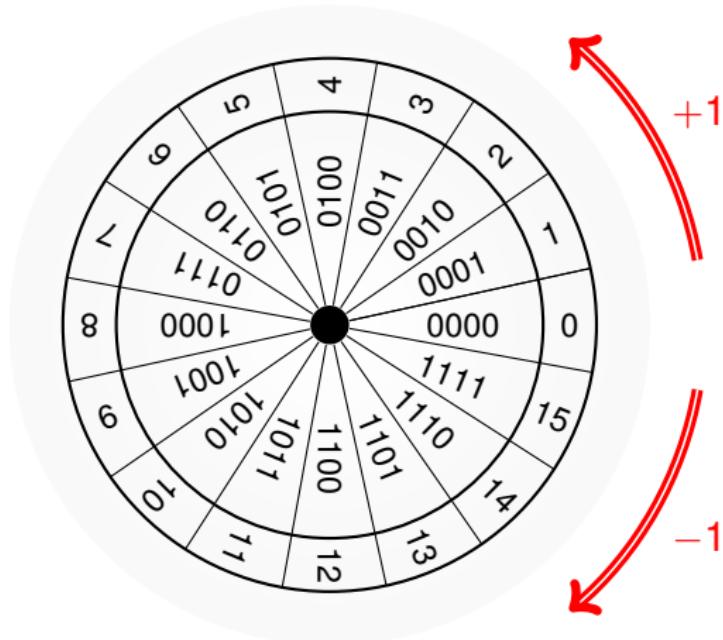

# Représentation binaire

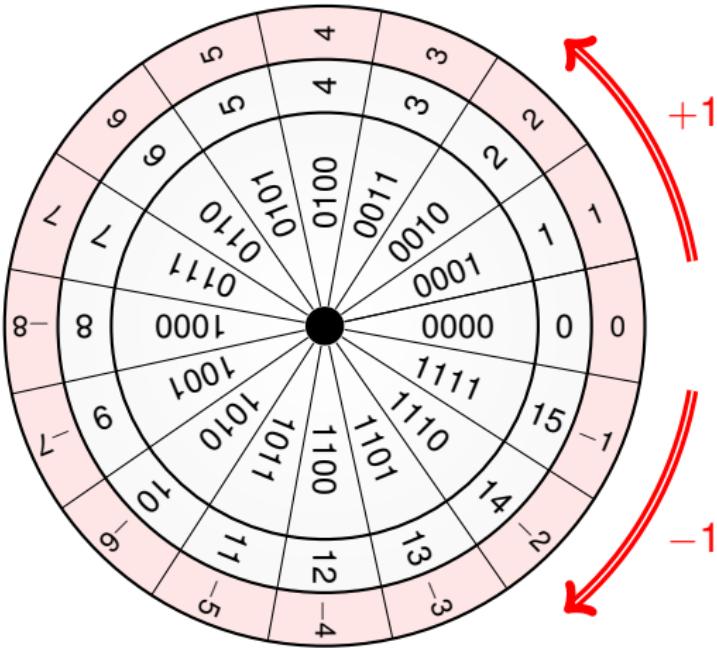

## Exemple sur 4 bits

- Avec 4 bits on peut représenter les nombres allant de 0 à  $15 = 2^4 - 1$

- L'arithmétique est alors modulo  $2^4 = 16$

- Par exemple :

- $15 + 1 = 0$

- $0 - 1 = 15$

| Décimal | Binaire |

|---------|---------|

| 0       | 0000    |

| 1       | 0001    |

| 2       | 0010    |

| 3       | 0011    |

| 4       | 0100    |

| 5       | 0101    |

| 6       | 0110    |

| 7       | 0111    |

| 8       | 1000    |

| 9       | 1001    |

| 10      | 1010    |

| 11      | 1011    |

| 12      | 1100    |

| 13      | 1101    |

| 14      | 1110    |

| 15      | 1111    |

# Représentation binaire

## Exemple sur 4 bits

- Avec 4 bits on peut représenter les nombres allant de 0 à  $15 = 2^4 - 1$

- L'arithmétique est alors modulo  $2^4 = 16$

- Par exemple :

- $15 + 1 = 0$

- $0 - 1 = 15$

- Comment conserver le même comportement et représenter des nombres signés ?

| Décimal | Binaire |

|---------|---------|

| 0       | 0000    |

| 1       | 0001    |

| 2       | 0010    |

| 3       | 0011    |

| 4       | 0100    |

| 5       | 0101    |

| 6       | 0110    |

| 7       | 0111    |

| 8       | 1000    |

| 9       | 1001    |

| 10      | 1010    |

| 11      | 1011    |

| 12      | 1100    |

| 13      | 1101    |

| 14      | 1110    |

| 15      | 1111    |

# Représentation binaire des nombres

Les nombres entiers signés : exemple sur 4 bits

# Représentation binaire des nombres

## Les nombres entiers signés : exemple sur 4 bits

# Représentation binaire des nombres

## Représentation en complément à 2 (CA2)

La valeur d'un nombre en CA2 sur  $n$  bits

$$A = -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i$$

- C'est une **interprétation** du mot binaire.

- Le bit de poids fort représente le signe

- 0 → nombre positif =  $\sum_{i=0}^{n-2} a_i 2^i$

- 1 → nombre négatif =  $-2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i$

- Permet de représenter les nombres dans l'intervalle  $[-2^{n-1}, 2^{n-1} - 1]$

# Représentation binaire

## Entiers relatifs sur 4 bits

- Avec 4 bits on peut représenter les nombres allant de  $-8$  à  $7$

- càd  $[-(2^3), 2^3 - 1]$

| Décimal | Binaire | Signé |

|---------|---------|-------|

| 0       | 0000    | 0     |

| 1       | 0001    | 1     |

| 2       | 0010    | 2     |

| 3       | 0011    | 3     |

| 4       | 0100    | 4     |

| 5       | 0101    | 5     |

| 6       | 0110    | 6     |

| 7       | 0111    | 7     |

| 8       | 1000    | -8    |

| 9       | 1001    | -7    |

| 10      | 1010    | -6    |

| 11      | 1011    | -5    |

| 12      | 1100    | -4    |

| 13      | 1101    | -3    |

| 14      | 1110    | -2    |

| 15      | 1111    | -1    |

# Exemples

## ■ Représentez -8 et +8

- en utilisant 4 bits

- en utilisant 5 bits

# Exemples

- Représentez -8 et +8

- en utilisant 4 bits

- en utilisant 5 bits

- Représentez -1

- en utilisant 1 bit

- en utilisant 2 bits

- en utilisant 3 bits ...

# Représentation binaire des nombres

## Extension de signe pour le CA2

Soit  $N = (a_{n-1}, a_{n-2}, \dots, a_0)_{\text{CA2}/n}$  un entier relatif représenté en CA2 sur  $n$  bits.

Comment représenter  $N$  sur  $n + 1$  bits.

$$\begin{aligned} N &= -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i \\ &= -a_{n-1}2^{n-1} \cdot (2 - 1) + \sum_{i=0}^{n-2} a_i 2^i \\ N &= -a_{n-1}2^n + \sum_{i=0}^{n-1} a_i 2^i \end{aligned}$$

D'où  $N = (a_{n-1}, a_{n-1}, a_{n-2}, \dots, a_0)_{\text{CA2}/n+1}$

On a dupliqué le bit de poids fort, on parle d'extension de signe.

# Représentation binaire des nombres

## Les nombres en virgule fixe

Un nombre décimal  $D$  en base 2 peut être approximé par un vecteur  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0, a_{-1} \dots a_{-m})$  tel que :

$$D = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \dots + a_1 \cdot 2^1 + a_0 \cdot 2^0 + a_{-1} \cdot 2^{-1} + \dots + a_{-m} \cdot 2^{-m}$$

Où :

- Division implicite par  $2^m$

- $(a_{n-1}, \dots, a_0)$  est la partie entière

- $(a_{-1}, \dots, a_{-m})$  est la partie fractionnaire

- $2^{-m}$  représente la précision de cette approximation

# Exemples

- Représentez 0.5, 3.625

# Exemples

- Représentez 0.5, 3.625

- Représentez 0.6

- en utilisant 1 bit

- en utilisant 3 bits

- en utilisant 5 bits

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

# Addition

## Exemple

Faire une addition en binaire sur 4 bits...

# Addition

## Exemple

Faire une addition en binaire sur 4 bits...

## Décomposition de l'addition

L'addition peut être décomposée en plusieurs additions élémentaires sur 1 bit

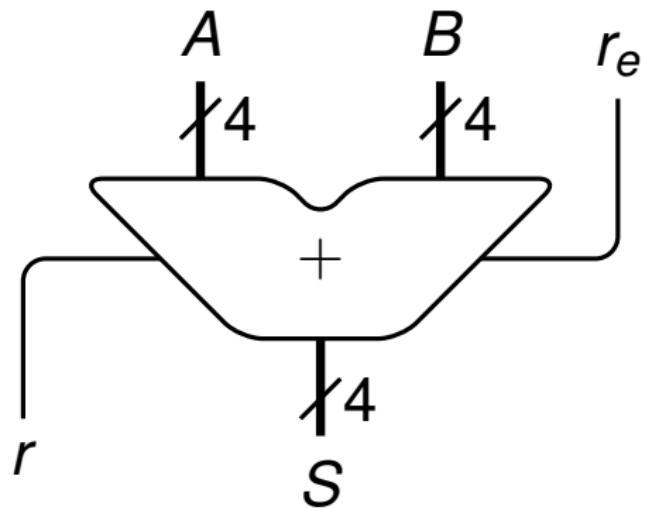

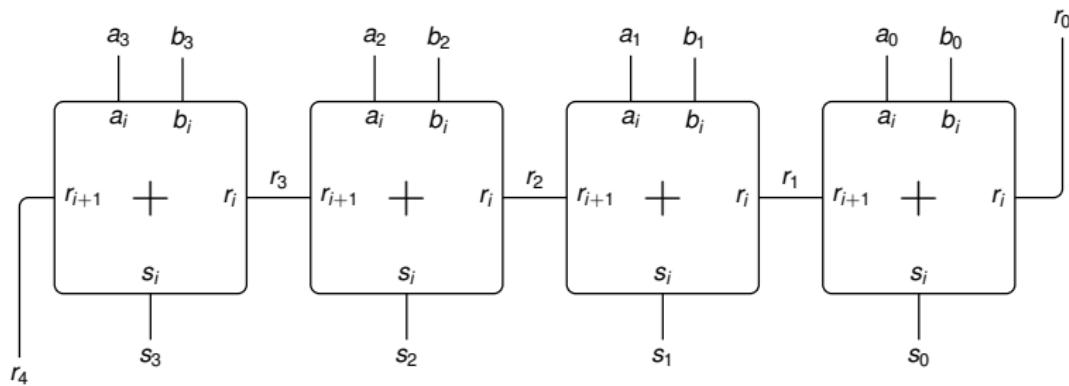

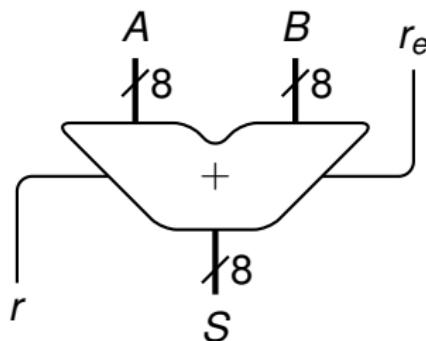

# Additionneur à propagation de retenue

# Additionneur à propagation de retenue

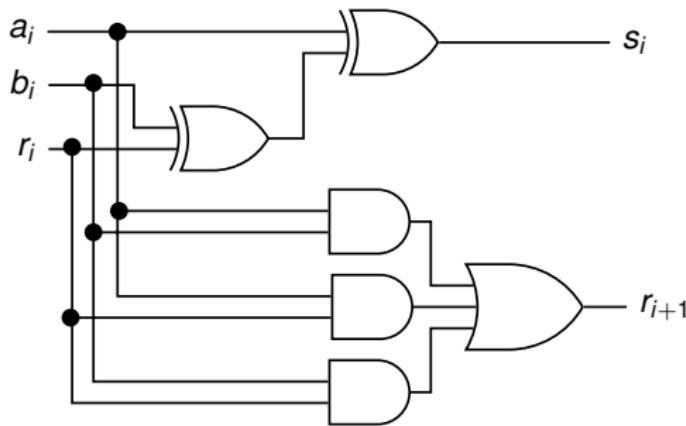

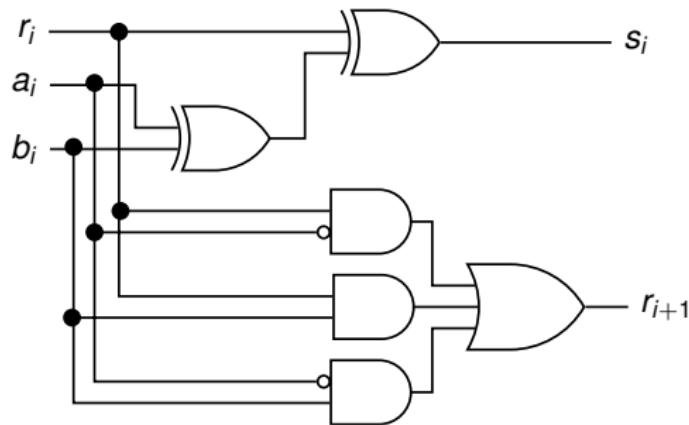

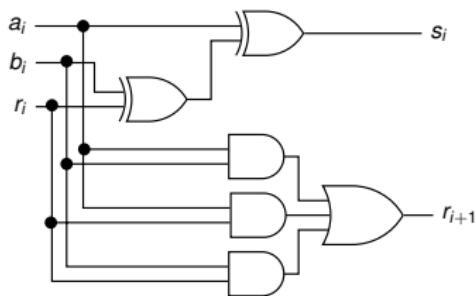

# Additionneur complet sur 1 bit

Arithmétiquement

$$a_i + b_i + r_i = 2 \cdot r_{i+1} + s_i$$

Table de vérité

| $a_i$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Décimal |

|-------|-------|-------|-----------|-------|---------|

| 0     | 0     | 0     | 0         | 0     | 0       |

| 0     | 0     | 1     | 0         | 1     | 1       |

| 0     | 1     | 0     | 0         | 1     | 1       |

| 0     | 1     | 1     | 1         | 0     | 2       |

| 1     | 0     | 0     | 0         | 1     | 1       |

| 1     | 0     | 1     | 1         | 0     | 2       |

| 1     | 1     | 0     | 1         | 0     | 2       |

| 1     | 1     | 1     | 1         | 1     | 3       |

# Additionneur complet sur 1 bit

$$s_i = a_i \oplus b_i \oplus r_i$$

$$r_{i+1} = a_i \cdot b_i + a_i \cdot r_i + b_i \cdot r_i$$

# Soustracteur complet sur 1 bit

Table de vérité

| $a_i$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Décimal |

|-------|-------|-------|-----------|-------|---------|

| 0     | 0     | 0     | 0         | 0     | 0       |

| 0     | 0     | 1     | 1         | 1     | -1      |

| 0     | 1     | 0     | 1         | 1     | -1      |

| 0     | 1     | 1     | 1         | 0     | -2      |

| 1     | 0     | 0     | 0         | 1     | 1       |

| 1     | 0     | 1     | 0         | 0     | 0       |

| 1     | 1     | 0     | 0         | 0     | 0       |

| 1     | 1     | 1     | 1         | 1     | -1      |

# Soustracteur complet sur 1 bit

Arithmétiquement

$$a_i - b_i - r_i = -2 \cdot r_{i+1} + s_i$$

Table de vérité

| $a_i$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Décimal |

|-------|-------|-------|-----------|-------|---------|

| 0     | 0     | 0     | 0         | 0     | 0       |

| 0     | 0     | 1     | 1         | 1     | -1      |

| 0     | 1     | 0     | 1         | 1     | -1      |

| 0     | 1     | 1     | 1         | 0     | -2      |

| 1     | 0     | 0     | 0         | 1     | 1       |

| 1     | 0     | 1     | 0         | 0     | 0       |

| 1     | 1     | 0     | 0         | 0     | 0       |

| 1     | 1     | 1     | 1         | 1     | -1      |

# Soustracteur complet sur 1 bit

$$s_i = a_i \oplus b_i \oplus r_i$$

$$r_{i+1} = \overline{a_i} \cdot b_i + \overline{a_i} \cdot r_i + b_i \cdot r_i$$

# Exercice

- Pour un bit  $b$  exprimez “logiquement” en fonction de  $b$  le résultat du calcul arithmétique  $1 - b$ .

- $A$  est un nombre signé codé en CA2 sur  $n$  bits. Montrez que  $-A = \bar{A} + 1$  (ici  $+$  est l’addition arithmétique)

- Proposez alors l’architecture d’un soustracteur utilisant un additionneur à propagation de retenue et des portes logique supplémentaires.

- Proposez l’architecture d’un additionneur/soustracteur commandé.

# Dynamique de l'addition

## Dépassement de capacité pour l'addition

### Nombres positifs

Pour deux nombres  $A$  et  $B$  représentés sur  $n$  bits nous avons :

$$\begin{aligned} A &\leq 2^n - 1 \\ B &\leq 2^n - 1 \\ A + B &\leq 2^{n+1} - 2 < 2^{n+1} \end{aligned}$$

$A + B$  est toujours représentable sur  $n + 1$  bits.

exemple :

$$\begin{array}{r} & 1 & 1 & 1 & (7) \\ + & 0 & 0 & 1 & (1) \\ \hline = & 1 & 0 & 0 & 0 & (8) \end{array}$$

# Dynamique de l'addition

## Dépassement de capacité pour l'addition

### CA2

Pour deux nombres  $A$  et  $B$  représentés en CA2 sur  $n$  bits nous avons :

$$\begin{array}{rclcrcl} -2^{n-1} & \leq & A & \leq & 2^{n-1} - 1 \\ -2^{n-1} & \leq & B & \leq & 2^{n-1} - 1 \\ -2^n & \leq & A + B & \leq & 2^n - 2 < 2^n \end{array}$$

$A + B$  est toujours représentable sur  $n + 1$  bits.

# Dynamique de l'addition

## Dépassement de capacité pour l'addition

### Exemples en CA2

|   |   |   |   | non signé | CA2      |

|---|---|---|---|-----------|----------|

|   | 1 | 1 | 1 | 7         | -1       |

| + | 0 | 0 | 1 | 1         | 1        |

| = | 1 | 0 | 0 | 8         | 0 ou -8? |

|   |   |   |   | non signé | CA2 |

|---|---|---|---|-----------|-----|

|   | 0 | 1 | 1 | 3         | 3   |

| + | 0 | 0 | 1 | 1         | 1   |

| = | 1 | 0 | 0 | 4         | -4  |

|   |   |   |   | non signé | CA2            |

|---|---|---|---|-----------|----------------|

|   | 1 | 1 | 1 | 7         | -1             |

| + | 1 | 0 | 0 | 4         | -4             |

| = | 1 | 0 | 1 | 11        | +3 + retenue ? |

En CA2 l'interprétation de la retenue n'est pas la même que pour les nombres non signés.

# Dynamique de l'addition

## Dépassement de capacité pour l'addition

CA2

Une solution simple pour toujours avoir le bon résultat est de d'abord étendre les nombres sur un bit de plus puis faire la somme.

La retenue produite au delà du bit ajouté n'est pas prise en compte.

$$\begin{array}{r} & 1 & 1 & 1 & 1 \\ + & 1 & 1 & 0 & 0 \\ \hline = & 1 & 0 & 1 & 1 \end{array} \left| \begin{array}{c} -1 \\ -4 \\ \hline -5 \end{array} \right.$$

$$\begin{array}{r} & 1 & 1 & 1 & 1 \\ + & 0 & 0 & 0 & 1 \\ \hline = & 0 & 0 & 0 & 0 \end{array} \left| \begin{array}{c} -1 \\ 1 \\ \hline 0 \end{array} \right.$$

# Plan

Traitement numérique de l'information

Signal électrique binaire

Logique Booléenne

Représentation des nombres

Opérateurs Arithmétiques

Notion de temps de propagation

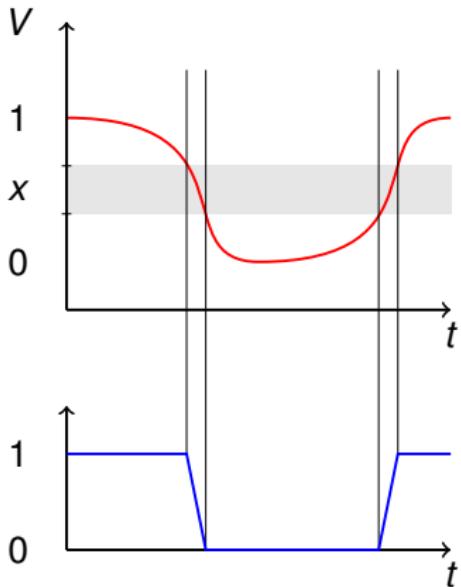

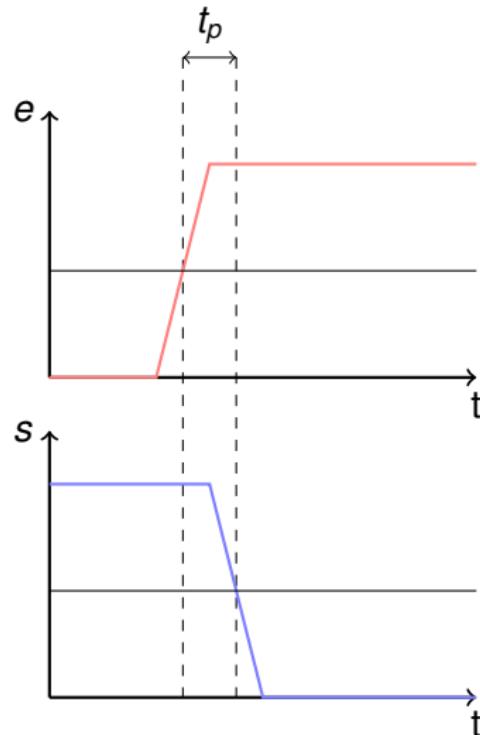

# Temps de propagation d'une porte

- Les portes logiques respectent les lois de la physique. Les changement d'état ne peuvent pas être instantanés.

- Le **temps de propagation** est le temps entre le changement des entrées d'une porte et la stabilisation de la valeur de sa sortie.

- La valeur de la sortie n'est valide qu'après ce temps.

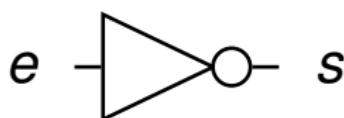

# Temps de propagation d'une porte

Exemple simple : Un inverseur

# Temps de propagation d'une porte

## Règles pour les portes complexes

- Les portes logiques de base sont pré-caractérisées.

- Pour une technologie particulière, on connaît le temps de propagation des portes de base.

- À partir de ces tables, on calcule le temps de propagation des portes complexes en faisant la somme des temps individuels des portes qui se suivent.

- Le temps de propagation d'une porte complexe est le temps de propagation du chemin le plus long.

# Temps de propagation d'une porte

Exemple : Full adder

- Considérons que le temps de propagation est de :

- 1 ns pour les portes AND et OR

- 2 ns pour les portes XOR

- Quel est le temps de propagation des entrées vers chaque sortie ?

# Temps de propagation d'une porte

Exemple : Carry adder

- Quel est le temps de calcul maximum d'un additionneur 8 bits à propagation de retenue ?

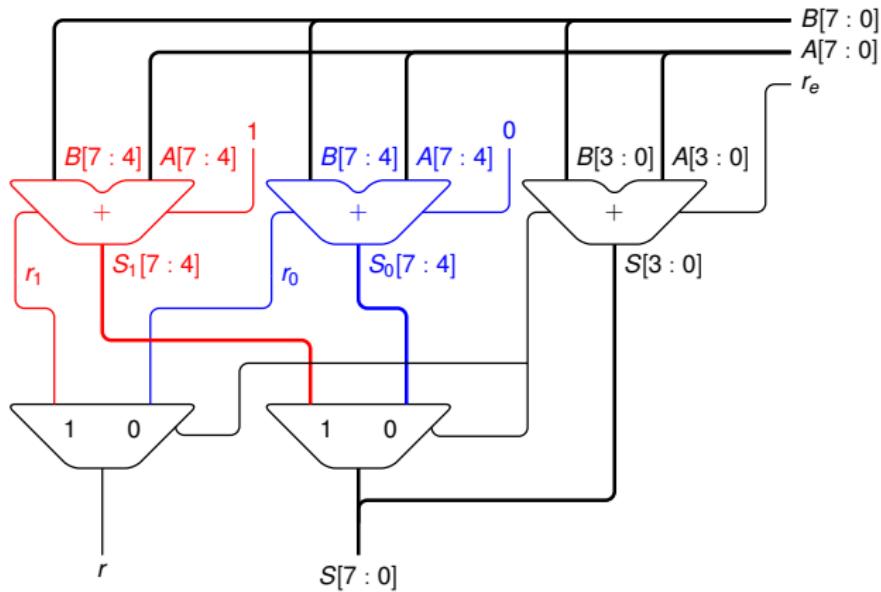

# Temps de propagation d'une porte

## Exemple 2

- Quelle est la fonction de ce montage ?

- Quels sont ses avantages et inconvénients ?

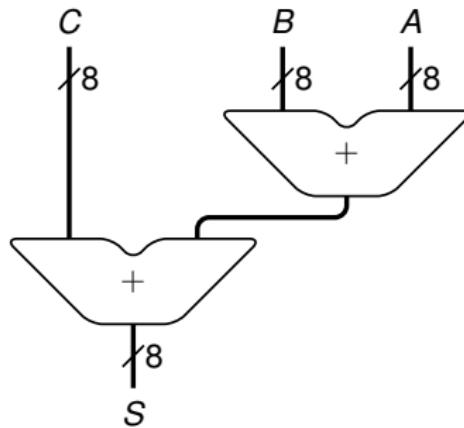

# Temps de propagation d'une porte

## Exemple 3

- Quel est le temps de propagation de cette addition ?

# Exercice

- Proposez 2 solutions pour construire un opérateur qui, pour 2 nombres non signés représentés sur 8 bits, renvoie le maximum.

- L'une utilisant un opérateur arithmétique

- L'autre comparant bit à bit les 2 nombres (en commençant par le poids fort)

- Quel est le temps de propagation dans chaque cas.

- Proposez dans chaque cas une architecture permettant de comparer 4 nombres. Quel est alors temps de propagation ?

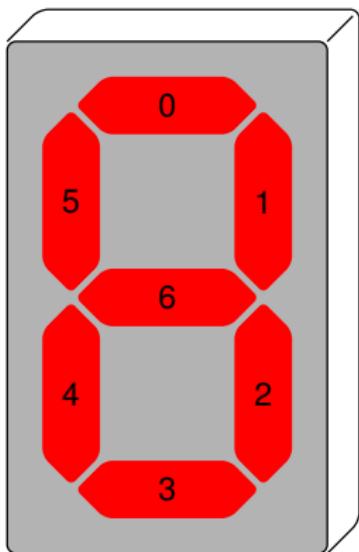

# À préparer pour la prochaine séance !

## Le décodeur 7 segments

- Permet d'afficher de l'hexadécimal (0,1,...,9,A,B...,F)

- L'entrée est sur 4 bits ( $0 \rightarrow F$ )

- La sortie est sur 7 bits

- Chaque bit contrôle un segment

- Si le bit est à 0 le segment est allumé

- Donnez les équations de chaque sortie