Institut

Mines-Télécom

# Les PCB

...conception, réalisation

Alexis Polti

# Licence de droits d'usage

Contexte académique } sans modification

*Par le téléchargement ou la consultation de ce document, l'utilisateur accepte la licence d'utilisation qui y est attachée, telle que détaillée dans les dispositions suivantes, et s'engage à la respecter intégralement.*

La licence confère à l'utilisateur un droit d'usage sur le document consulté ou téléchargé, totalement ou en partie, dans les conditions définies ci-après, et à l'exclusion de toute utilisation commerciale.

Le droit d'usage défini par la licence autorise un usage dans un cadre académique, par un utilisateur donnant des cours dans un établissement d'enseignement secondaire ou supérieur et à l'exclusion expresse des formations commerciales et notamment de formation continue. Ce droit comprend :

- le droit de reproduire tout ou partie du document sur support informatique ou papier,

- le droit de diffuser tout ou partie du document à destination des élèves ou étudiants.

Aucune modification du document dans son contenu, sa forme ou sa présentation n'est autorisé.

Les mentions relatives à la source du document et/ou à son auteur doivent être conservées dans leur intégralité.

Le droit d'usage défini par la licence est personnel, non exclusif et non transmissible.

Tout autre usage que ceux prévus par la licence est soumis à autorisation préalable et expresse de l'auteur :

[alexis.polti@telecom-paristech.fr](mailto:alexis.polti@telecom-paristech.fr)

# PCB : définitions

- **PCB : Printed Circuit Board (circuit imprimé) : empilement de couches de cuivre et d'isolants (substrat) destiné à recevoir les composants d'un système et à assurer leur interconnexion.**

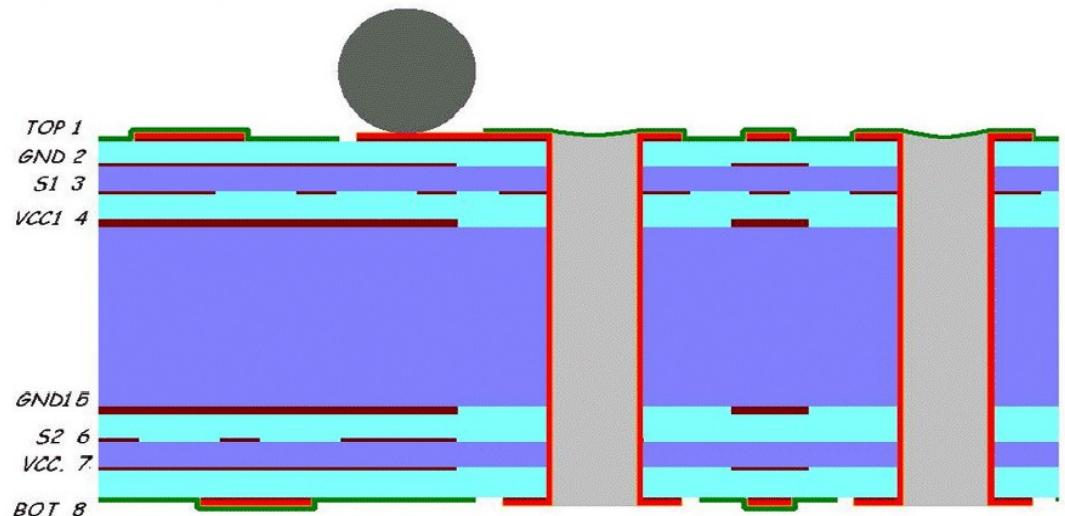

## PCB

- empilage de couches successives de

- cuivre (conducteur), sous forme de

- pistes

- pads (plages d'accueil des broches des composants)

- vias : interconnexions entre différentes couches

- isolant

- et en couches externes :

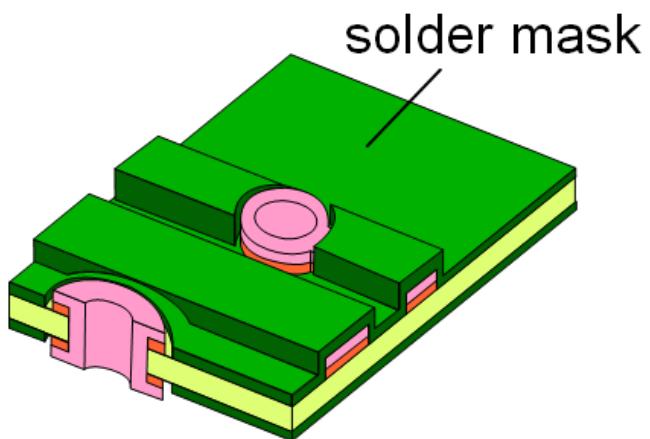

- vernis épargne (soldermask)

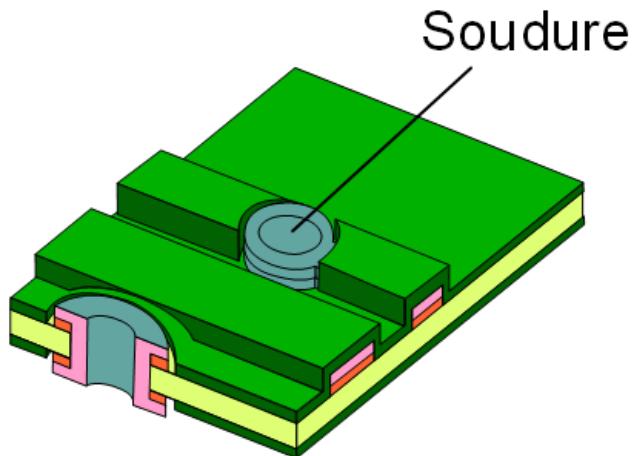

- pâte à braser (solderpaste)

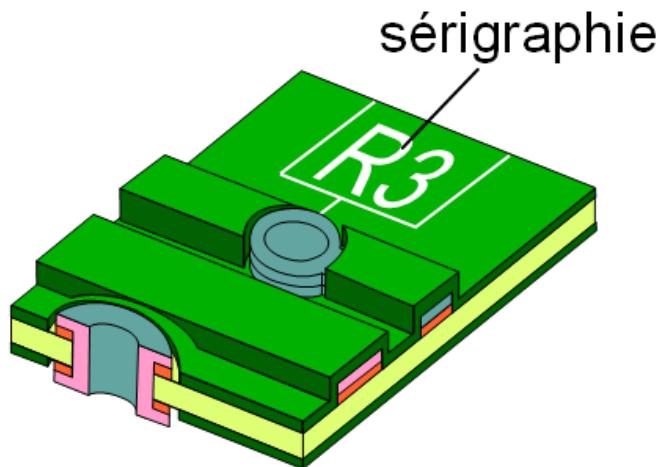

- sérigraphie

- nombre de couches

- 1

- 2

- $2n$

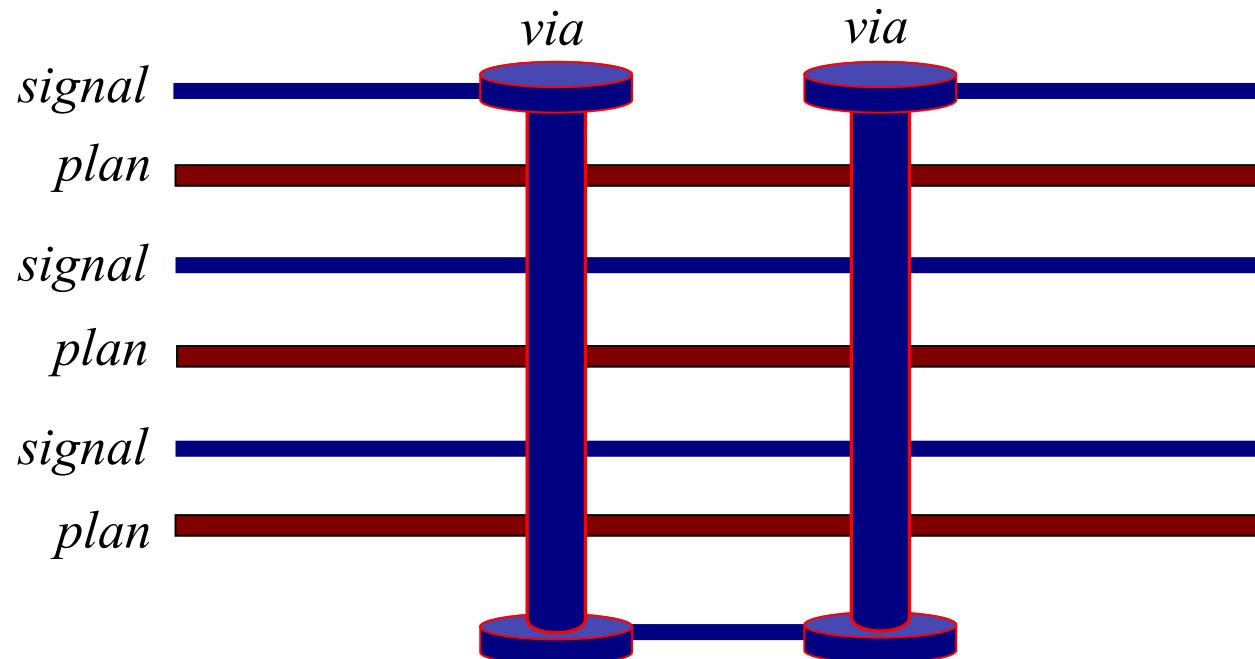

## PCB : les vias

- **Via : trou métallisé permettant d'interconnecter des pistes situées sur des couches différentes.**

- traversant / enterré / borgne

- standard / micro-via

- diamètres différents selon le type de couche(s) traversée(s)

- **Classes standards (norme NFC 93-713)**

| Critère                          | Classe |      |      |      |             |             |             |

|----------------------------------|--------|------|------|------|-------------|-------------|-------------|

|                                  | 1      | 2    | 3    | 4    | 5           | 6           | 7           |

| largeur minimale des conducteurs | 0.7    | 0.45 | 0.28 | 0.19 | <b>0.15</b> | <b>0.12</b> | <b>0.1</b>  |

| espace minimal entre conducteurs | 0.6    | 0.45 | 0.28 | 0.19 | <b>0.15</b> | <b>0.12</b> | <b>0.1</b>  |

| largeur des pastilles            |        | 1.65 | 1.25 | 1.05 | <b>0.85</b> | <b>0.65</b> | <b>0.55</b> |

| diamètre des trous traversants   |        | 0.8  | 0.7  | 0.6  | <b>0.45</b> | <b>0.35</b> | <b>0.3</b>  |

- Les constructeurs peuvent proposer / demander d'autres valeurs de largeur / isolement

- Les diamètres de perçages dépendent souvent de l'épaisseur du PCB

- Prendre en compte les tensions présentes dans les espacements (norme IPC)

- D'autres normes existent : IPC-A-600, MIL P55110, MIL P50884...

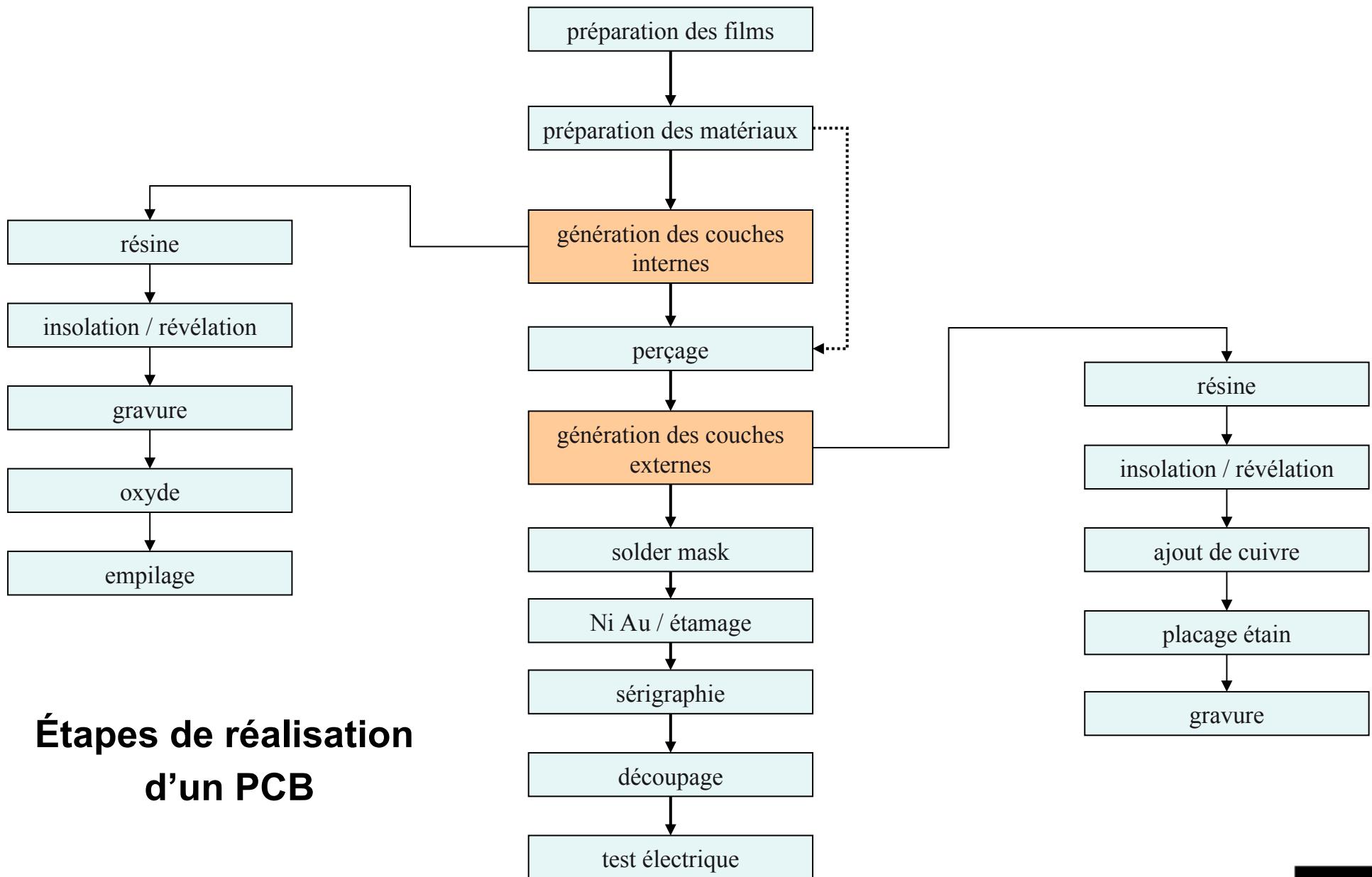

## PCB : réalisation

# Étapes de réalisation d'un PCB

- **Étapes préliminaires**

- Design rule check (DRC)

- Rectifications mineures

- Mise en panneaux

- Addition des coupons de tests

- Addition des « plating thieving »

- Préparation des films à partir des fichiers fournis

- Copper etching

- Solder mask

- Solder paste

- Sérigraphie

- **Fichiers à fournir**

- GERBER

- Fichiers de perçage (Excellion)

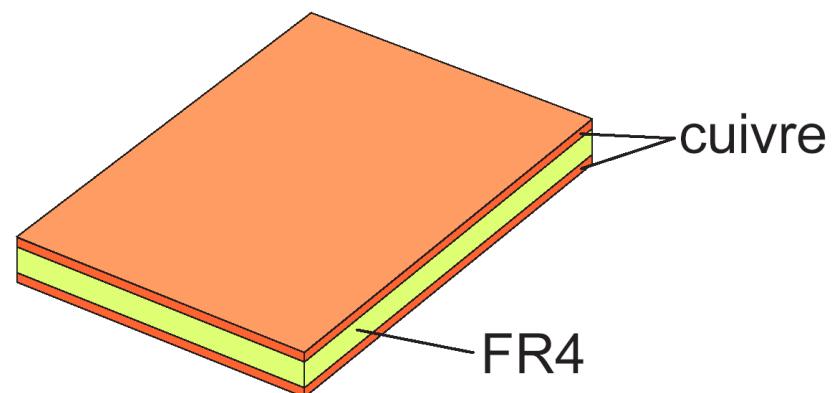

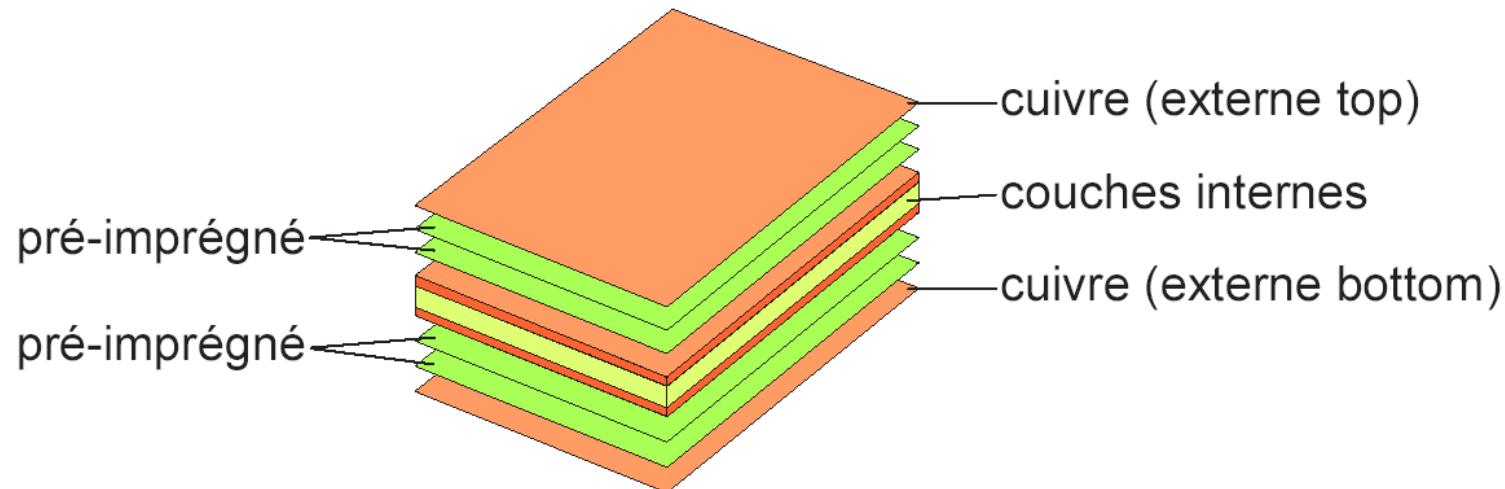

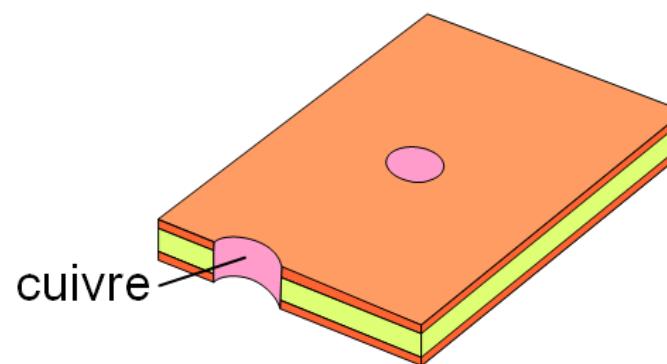

## 1. Préparation des matériaux

préparation des matériaux

- découpe des strates de cuivre / isolant

- découpe des isolants inter-strates (pré-imprégné)

- passage à l'étuve

- nettoyage de surface

## 2. Génération des couches internes

- préparation de l'empilage

génération de l'empilage

## 2. Génération des couches internes

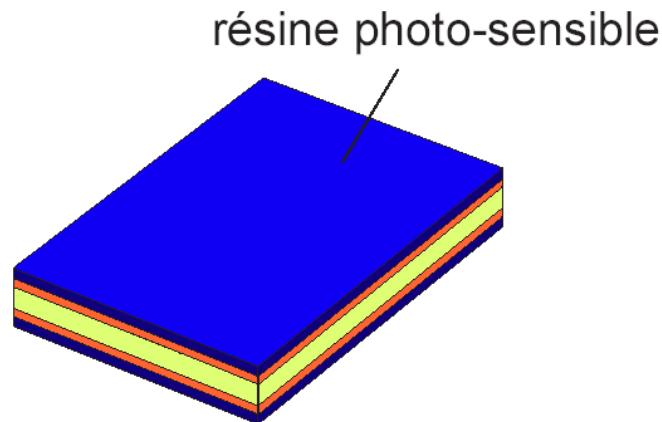

- dépôt de résine photosensible

génération de l'empilage

## 2. Génération des couches internes

- insolation aux UV

génération de l'empilage

# 2. Génération des couches internes

- révélation

génération de l'empilage

## 2. Génération des couches internes

- gravure puis suppression de la résine

génération de l'empilage

## 2. Génération des couches internes

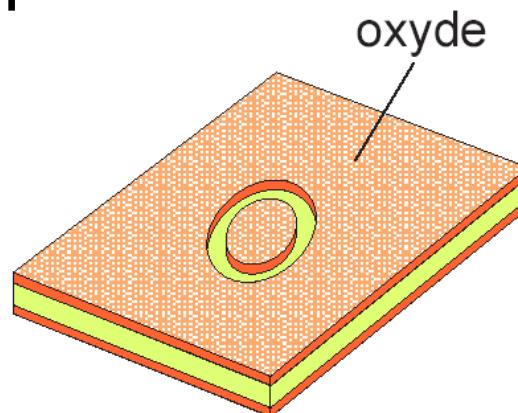

- phase d'oxydation

génération de l'empilage

## 2. Génération des couches internes

- réalisation de l'empilage

génération de l'empilage

## 2. Génération des couches internes

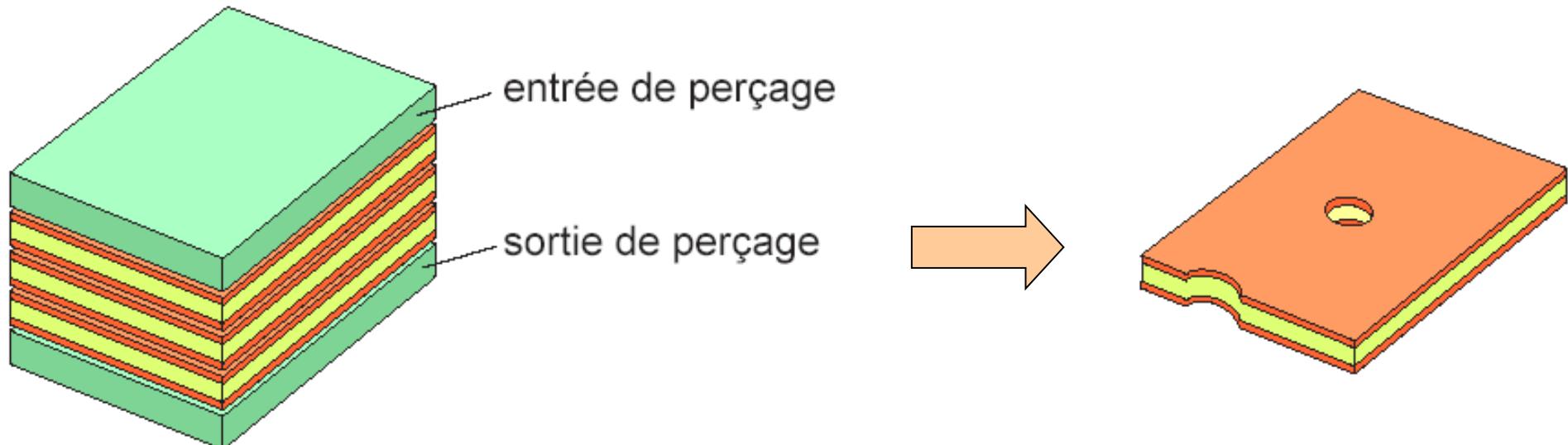

perçage

- perçage

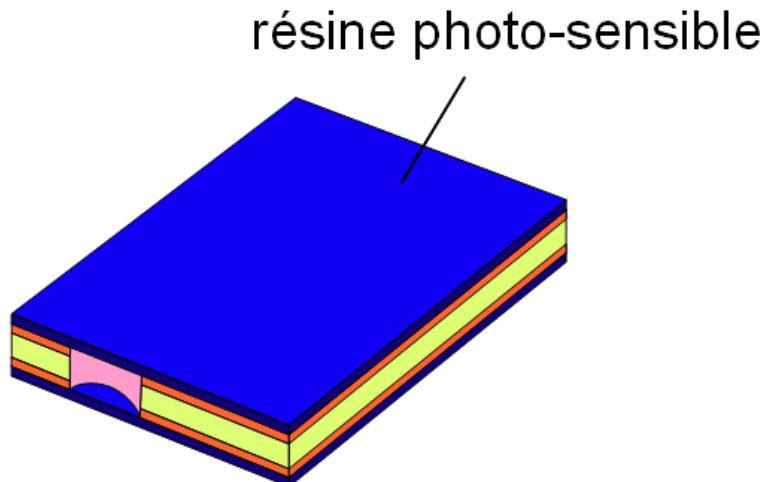

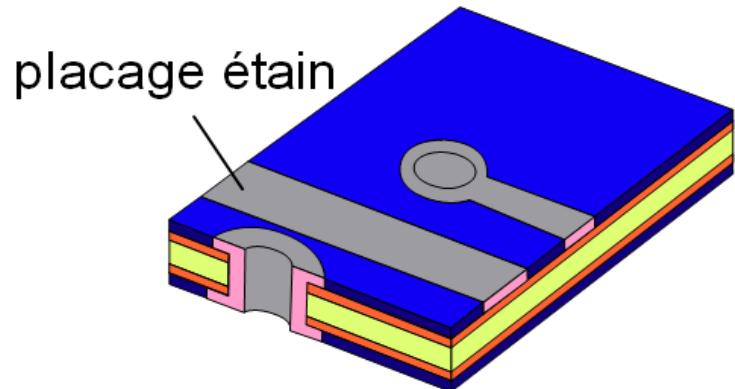

### 3. Génération des couches externes

génération des couches externes

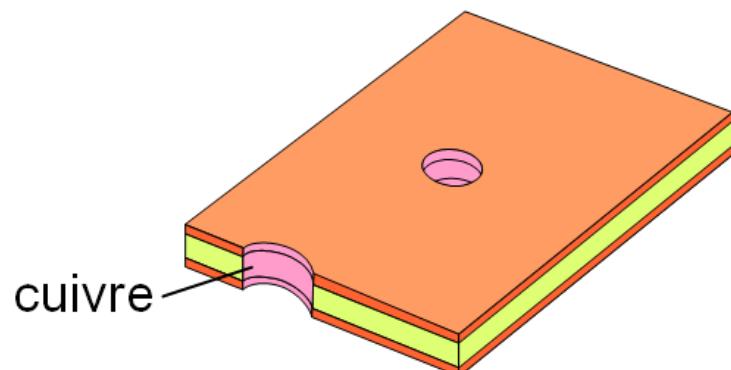

- nettoyage des trous et métallisation chimique

sans nettoyage

avec nettoyage

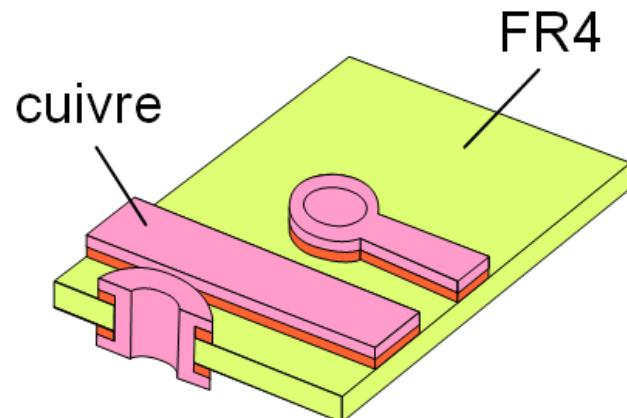

### 3. Génération des couches externes

- dépôt de résine photosensible

génération des couches externes

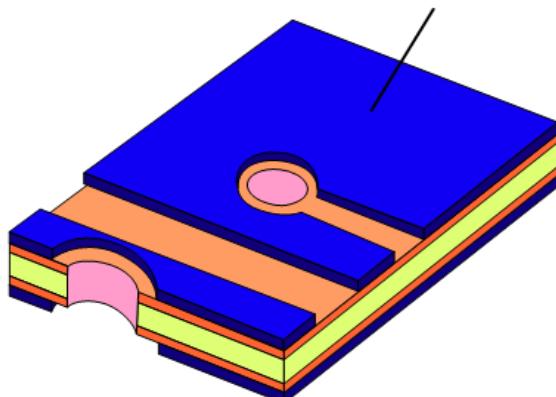

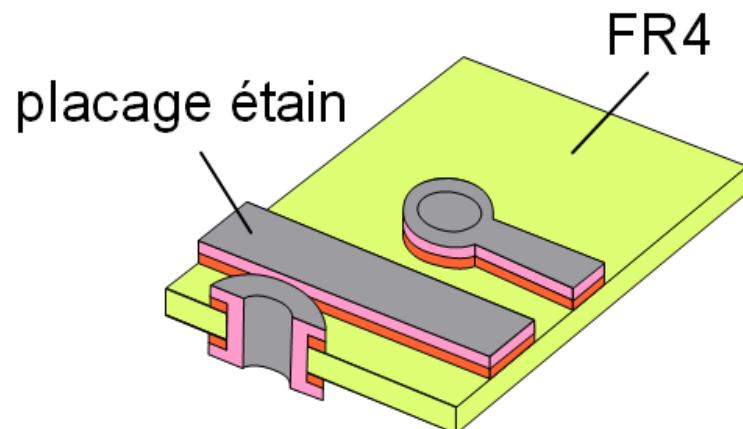

### 3. Génération des couches externes

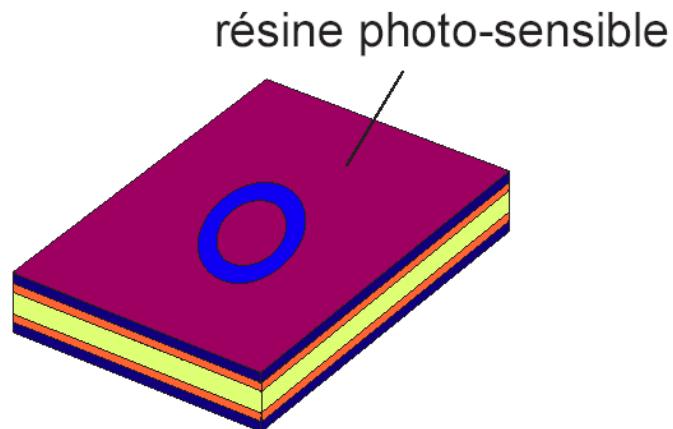

- **insolation / révélation**

résine photo-sensible

génération des couches externes

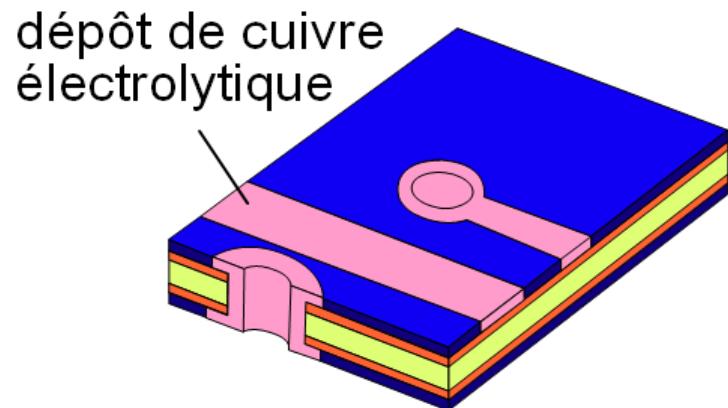

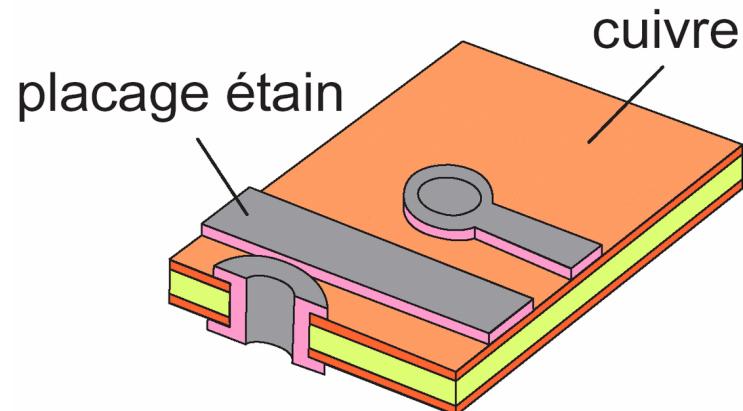

### 3. Génération des couches externes

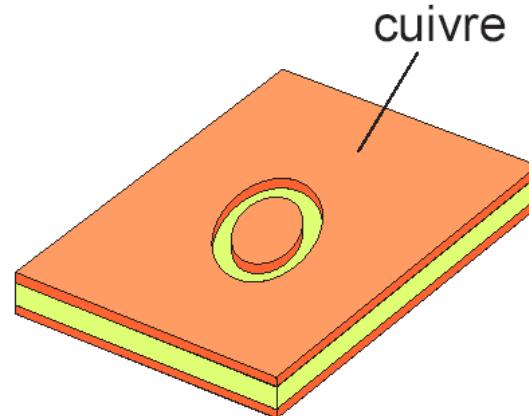

- placage électrique de cuivre

génération des couches externes

### 3. Génération des couches externes

- placage électrique d'étain

génération des couches externes

### 3. Génération des couches externes

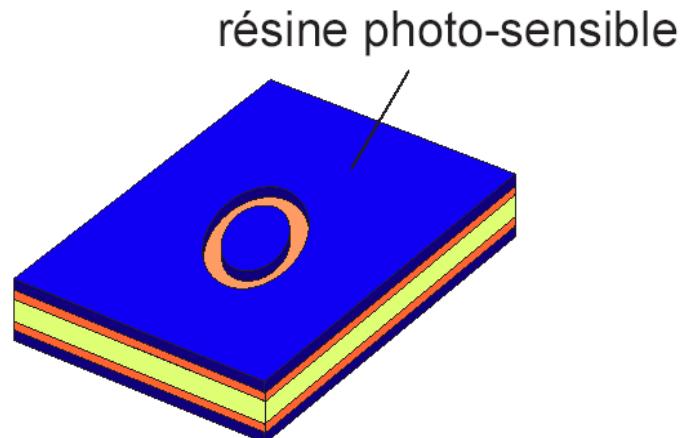

- suppression de la résine

génération des couches externes

### 3. Génération des couches externes

génération des couches externes

- gravure

### 3. Génération des couches externes

- suppression de l'étain

génération des couches externes

### 3. Génération des couches externes

- application du soldermask

génération des couches externes

### 3. Génération des couches externes

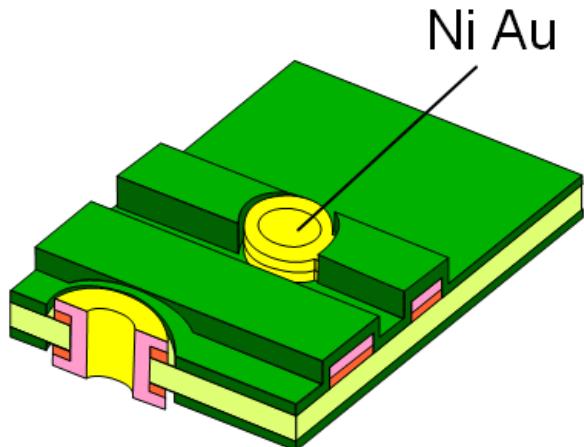

- placage nickel-or (ENIG), ou autre finition

génération des couches externes

### 3. Génération des couches externes

- étamage

génération des couches externes

### 3. Génération des couches externes

- sérigraphie

génération des couches externes

- découpage des panneaux

- inspection

- test électrique

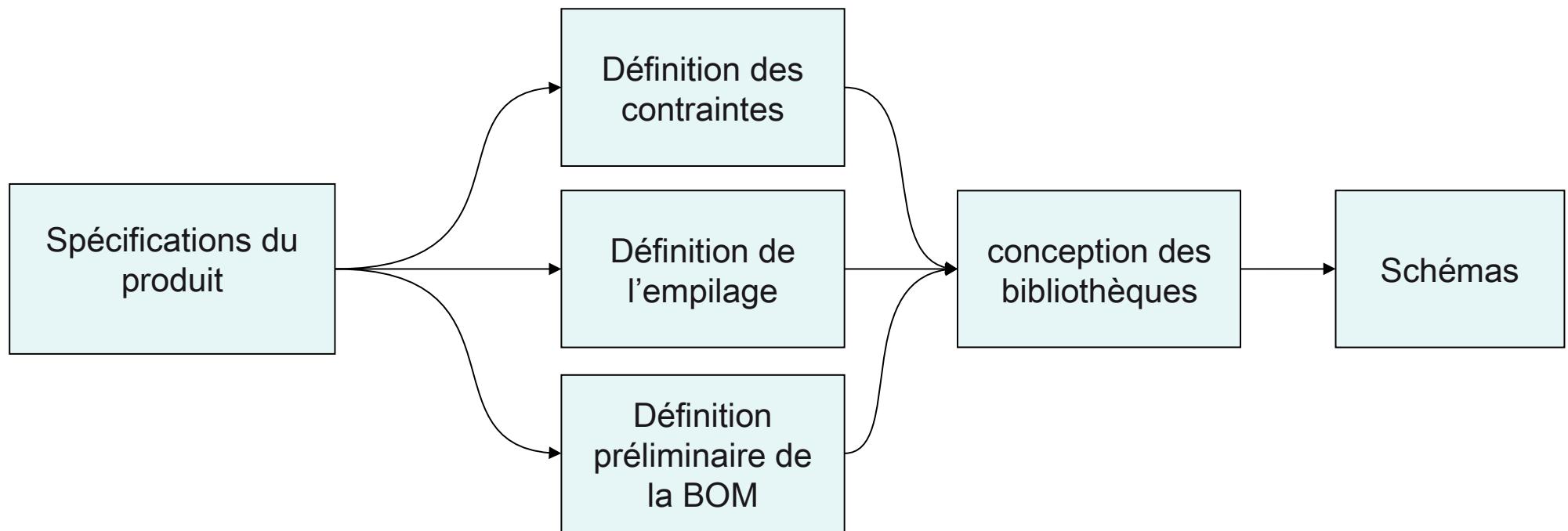

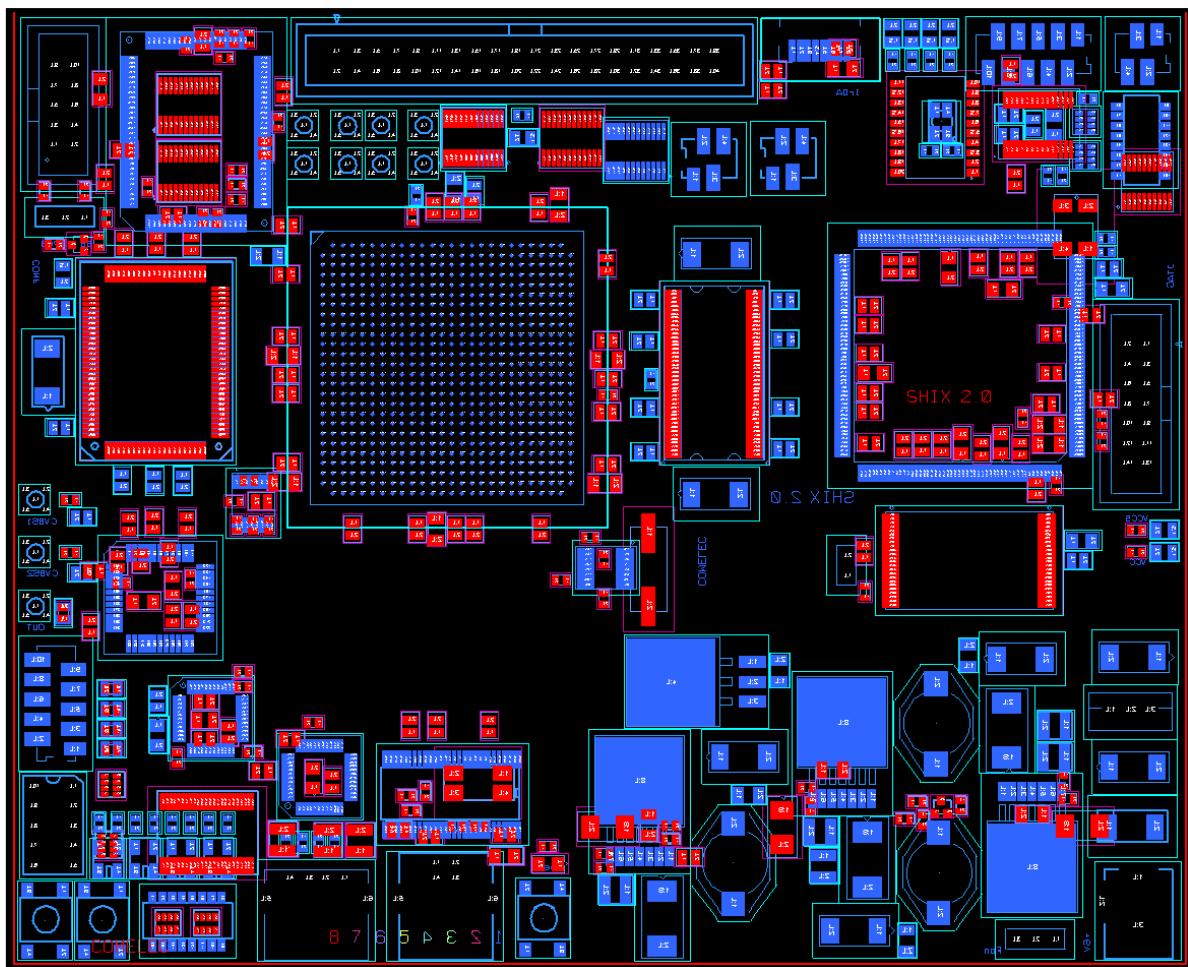

# PCB : flot de conception

- en 2 mots :

- Schéma :

- production des schémas

- création d'une netlist (liste des connexions et des composants)

- importation dans l'outil de CAO PCB

- PCB :

- import de la netlist

- placement des composants

- routage (traçage des pistes)

- production des fichiers de sortie

- rétro-annotation du schéma

# PCB : flot de conception

# PCB : flot de conception

## PCB :

- mise en place des contraintes non entrées dans les schémas

- placement

- fan out (sorties des composants)

- routage des nets critiques (horloges)

- routage

- génération des plans

- habillage

- DRC / ERC

- génération des fichiers de sortie

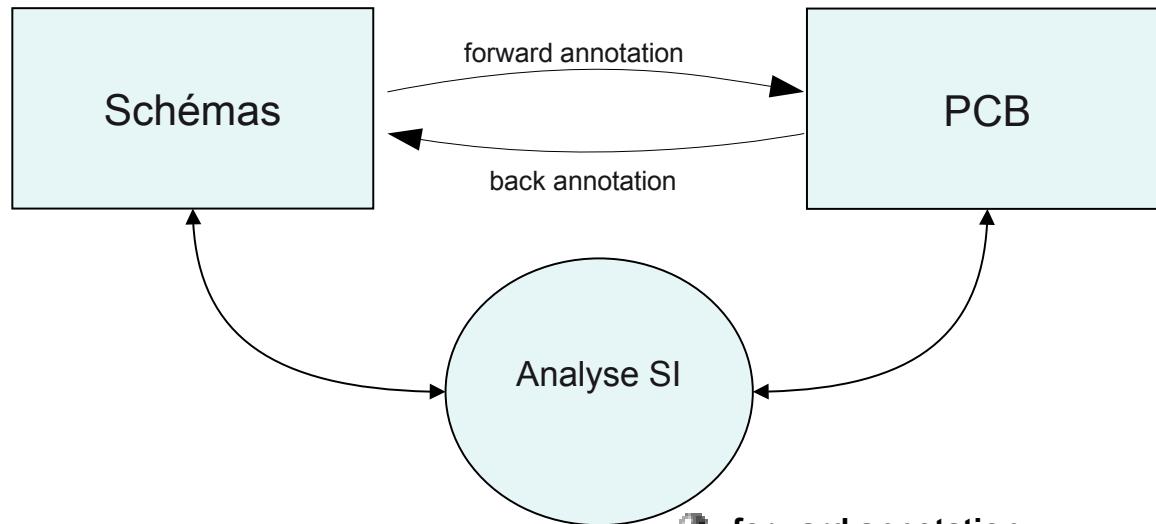

## forward annotation

- production ou changement de la netlist

- connexion

- composants

- topologie

- classe de net

- ## back annotation

- mise à jour des schémas

- topologie, contraintes

- référence (reference designator)

- swap (composants, portes, broches)

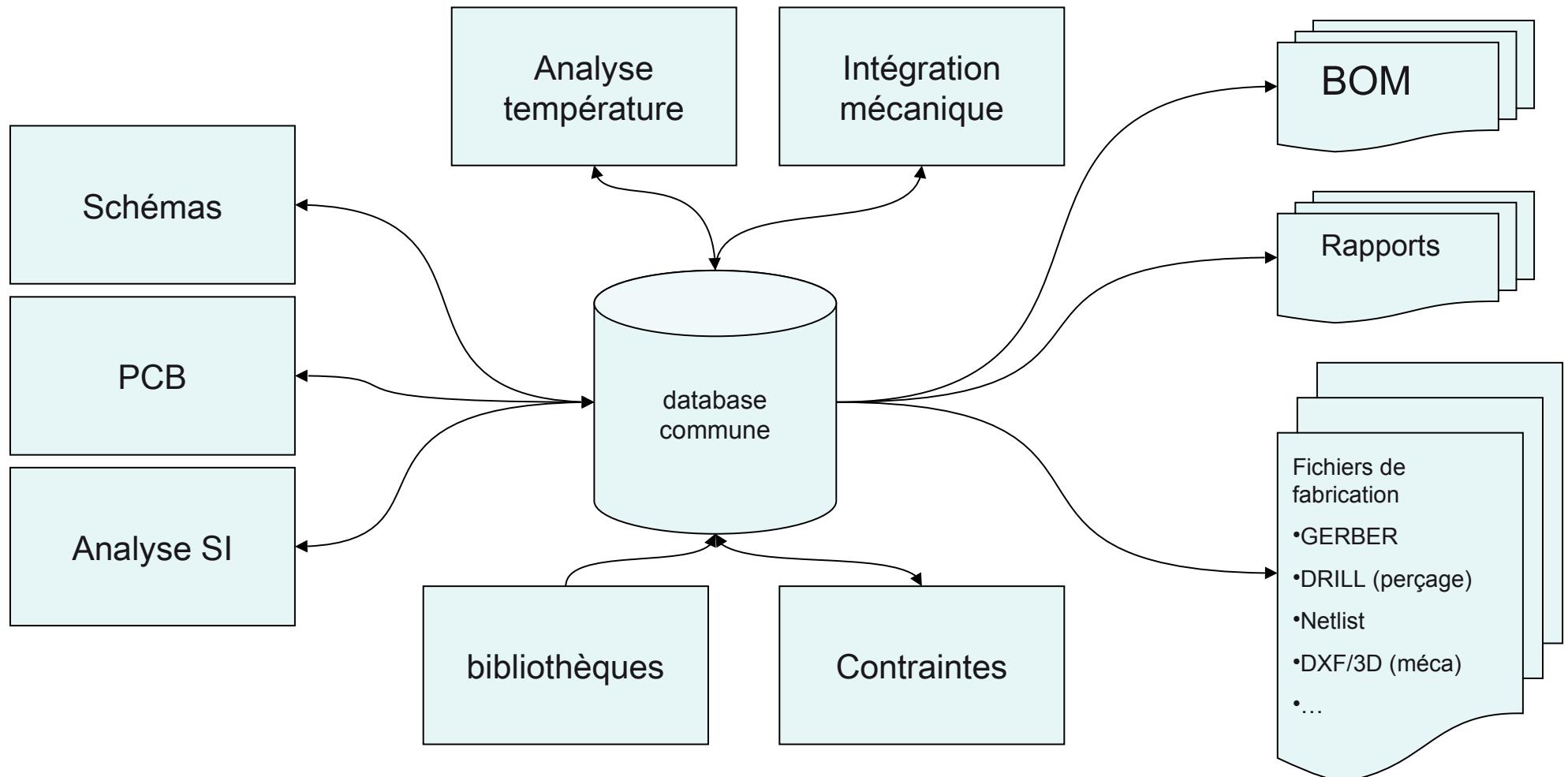

# PCB : flot de conception

**L'architecture du flot de conception doit être cohérente**

- **CAO Bibliothèques**

- unités, notations, ...

- symboles (symbols)

- empilages (padstacks)

- empreintes (footprints, cells, packages)

- composants (parts, devices)

- modèles (SPICE, IBIS)

- modèles de cartes

- blocs ré-utilisables

- ...

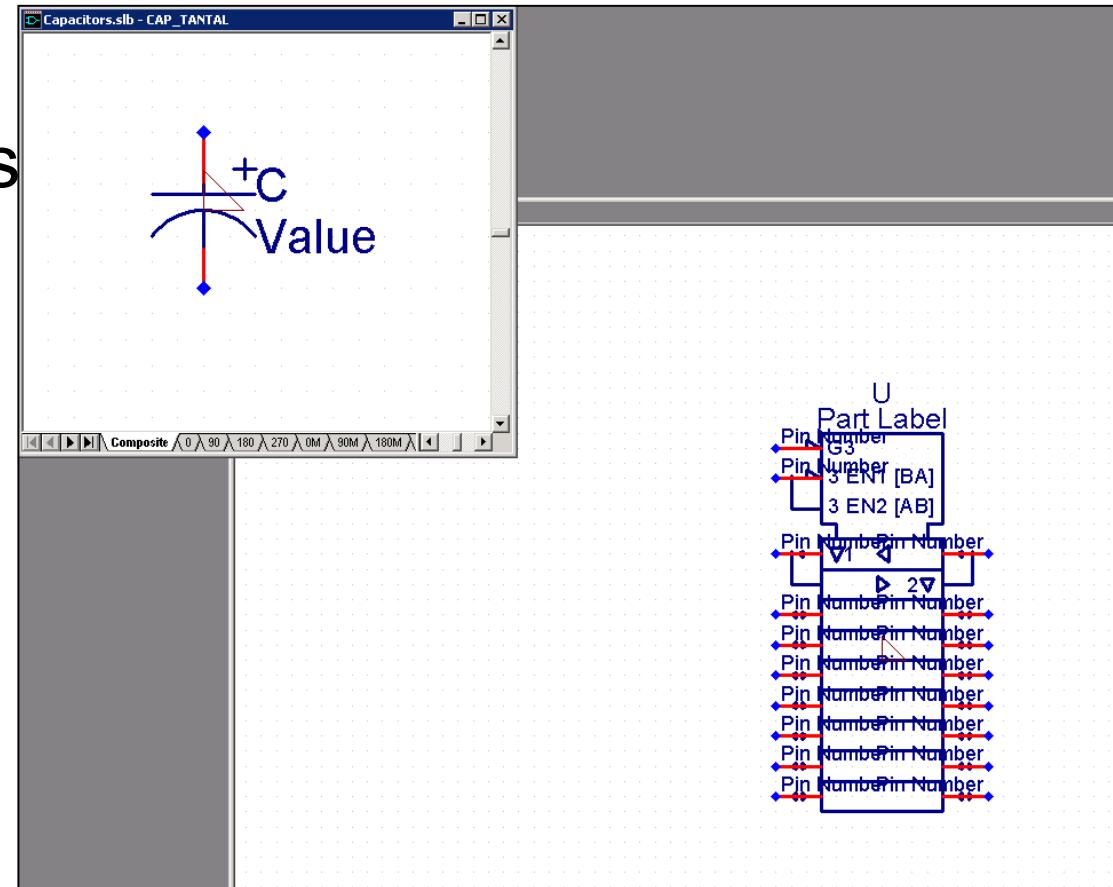

## Symboles

- purement logiques

- portes élémentaires

- champs fixes

- préfixe

- champs variables

- valeur

- part number

- description

- ...

# PCB : CAO (bibliothèques)

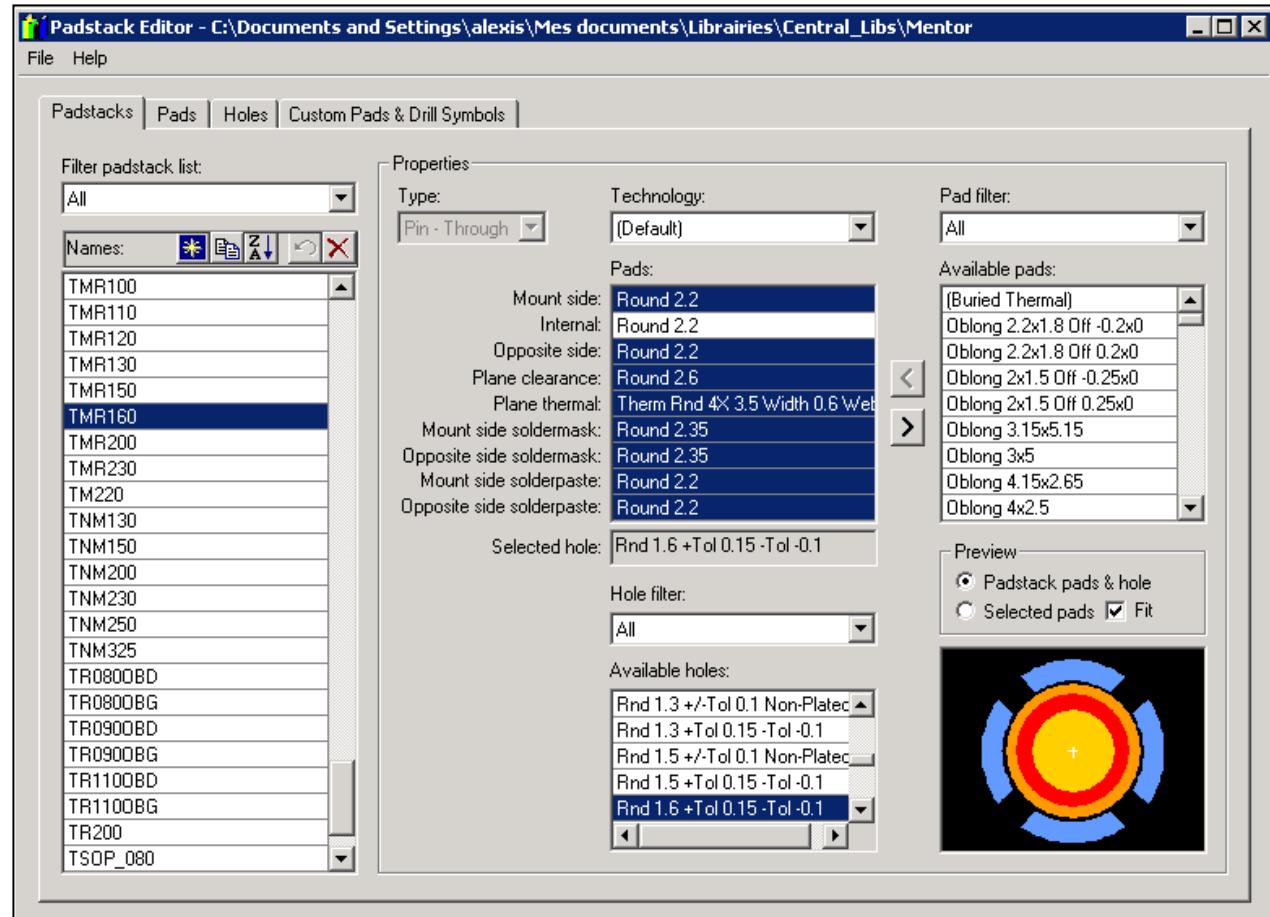

## Empilages

- composants

- vias

- mires (fiducials)

- trous de montage

# Empilages

- pads (pastilles) : ronds / rectangulaires

- top, bottom

- soldermask top, bottom

- solderpaste top, bottom

- couches internes (signaux + plans)

- pastilles spéciales

- thermals

- clearance

- 1 trou

- attention au diamètre (spécifié / fini)

- attribution d'un symbole de perçage (drill symbol)

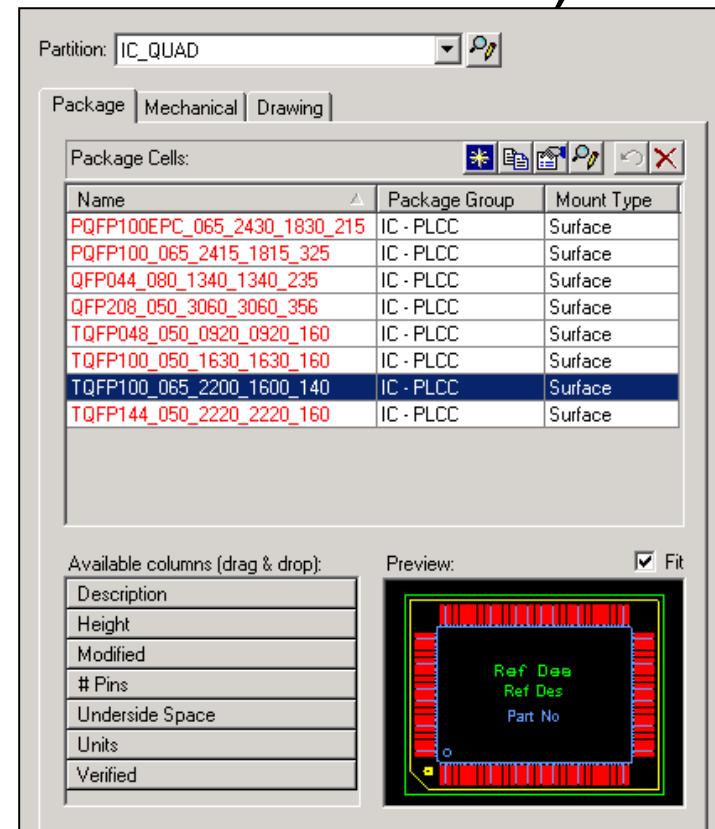

# Empreintes (cells, packages, footprints)

- pas d'informations logiques

- purement physique (numéros de broches)

- formées de

- padstacks

- contours

- obstructions

- texte (champs variables)

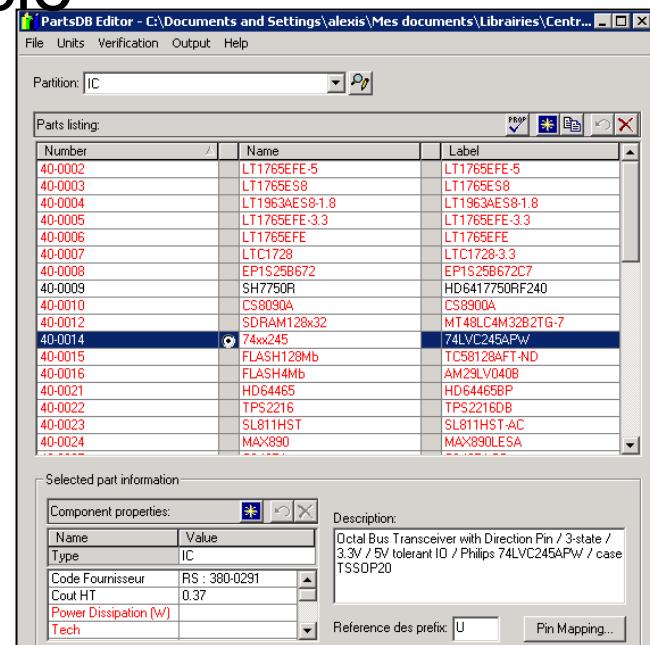

## Composants (parts, devices)

- mapping symboles / empreintes

- intègre éventuellement plusieurs portes

- éventuellement modèle IBIS associé

- propriétés utilisateurs

- référence fabricant

- prix

- code fournisseur / interne

- ...

- définit le mapping pins / pads

- définit les informations de swapping

# CAO Bibliothèques

- importance des bibliothèques

- fréquemment job à part entière

- processus de création de composants souvent complexes

- création de l'entrée

- validation des modèles

- contrôle

- vérification auprès des achats

- AVL (Approved Vendor List)

- ...

# CAO Schémas

- les schémas doivent être **complets**

- références

- valeur

- tension / précision / diélectrique / ...

- description

- code fournisseur / code interne

- prix

- lien vers datasheet

- ...

# CAO Schémas

- entrées des contraintes

- placement des composants / symboles

- connexions, mise en place des propriétés topologiques

- vérifications électriques (ERC)

- éventuellement mise en boîte (packaging)

- création de la netlist (forward annotation)

# CAO Schémas

- Entrées des contraintes

- sources / charges / terminaisons, topologies

- classes de nets (équipotentielles)

- Quelles contraintes ?

- espacements, largeur des pistes

- par classe

- signaux globaux (VDD, GND, ...)

- bibliothèques à utiliser

- divers fichiers de configuration

## CAO Schémas

- Placement des composants / symboles

- grouper les composants par fonction

- composants spéciaux (points de test)

- Connexion

- utiliser les connexions par noms

- utiliser les bus

- utiliser les schémas hiérarchiques

- utiliser les références croisées (renvois de pages)

- Utiliser des commentaires

- Variantes

- options (automatisables)

- commentaires, DNP (manuels)

# CAO Schémas

- Vérifications électriques (ERC)

- Éventuellement mise en boîte (packaging)

- remplacement des symboles par le part correspondant

- regroupement des composants multi-symboles

- assignation d'instances aux composants virtuels

- mise à jour des propriétés au passage

- numérotation des références

- Crédit à la netlist

- format propriétaire

- EDIF

- Verilog / VHDL / ...

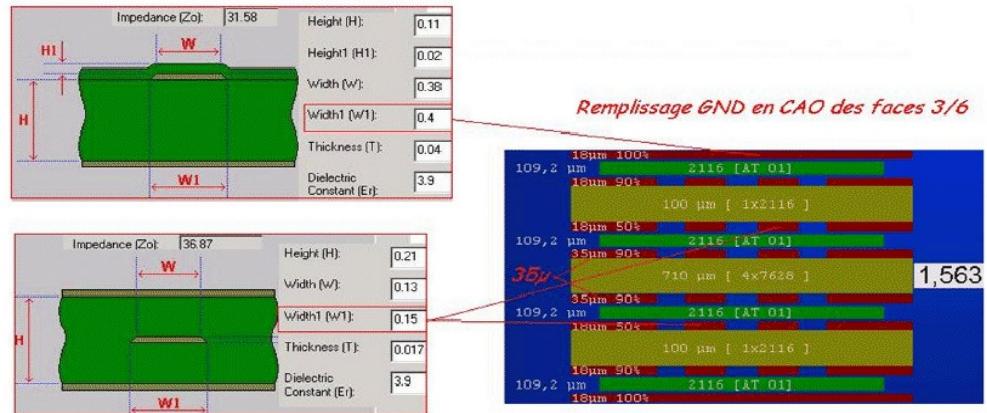

## CAO PCB

- Entrée des contraintes

- empilage

- impédance caractéristiques

- besoin de plans d'alimentations

- faisabilité

- placement

- règles d'assemblage

- maniabilité (connecteurs sur les bords...)

- minimisation des distances Manhattan

- séparation des zones bruitées / sensibles

- découplage

- répartition du poids / dissipation thermique

- routage

- topologies : ordre de connexion des composants

- parallélisme : diaphonie (crosstalk)

- paires différentielles

- temps de propagation / longueur

- overshoot / undershoot

# PCB : définition des empilages

- Doivent être équilibrés (symétriques) : nombre pair de couches.

- Déterminent l'impédance caractéristiques des pistes (cf. cours intégrité du signal)

- Nécessité d'avoir une couche plan adjacente à chaque couche piste.

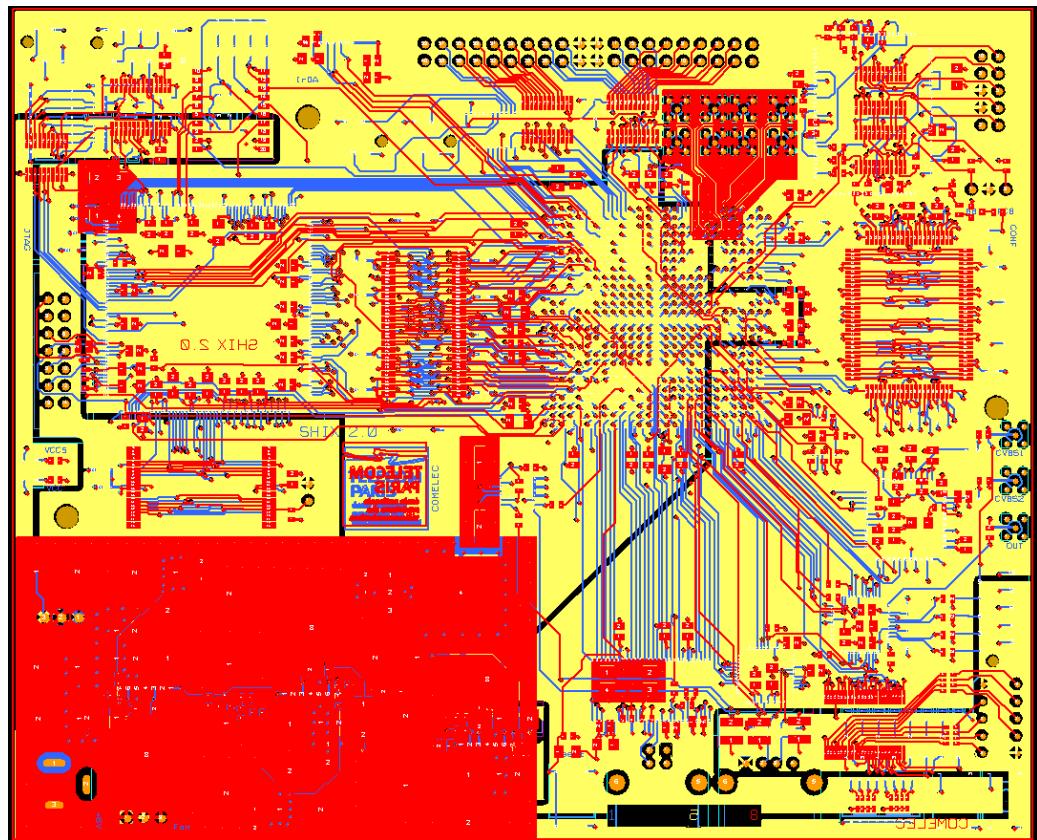

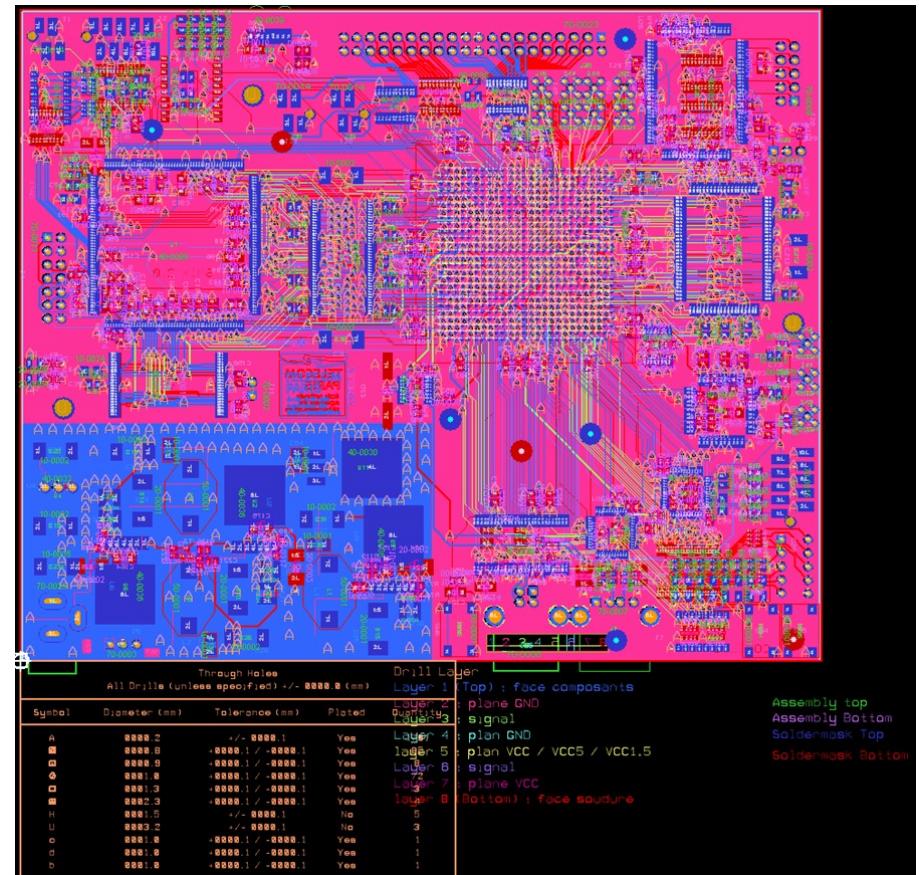

ENST, ENST SH4, 050203

MCB, FR4, 1.6 mm, classe 5, NI/AU, 2VE, 2SE, 150 x 120 mm BGA 1.27/672 pts, Vias 0.35/0.7

# PCB : les couches

## ● Couches critiques

- routage

- fabrication

- soldermask

- solderpaste

- drill

## ● Éléments de dessin

- outline

- contours

- mires (fiducials)

- origine

- bordures de routage

- obstructions

- zones

## ● Placement

- placement outlines

- insertion outline

- obstructions

## ● Assemblage

- outline

- textes

## ● Sérigraphie (silkscreen)

- outlines

- textes

- avant et après génération

## ● Éléments spéciaux

- vias

- points de test

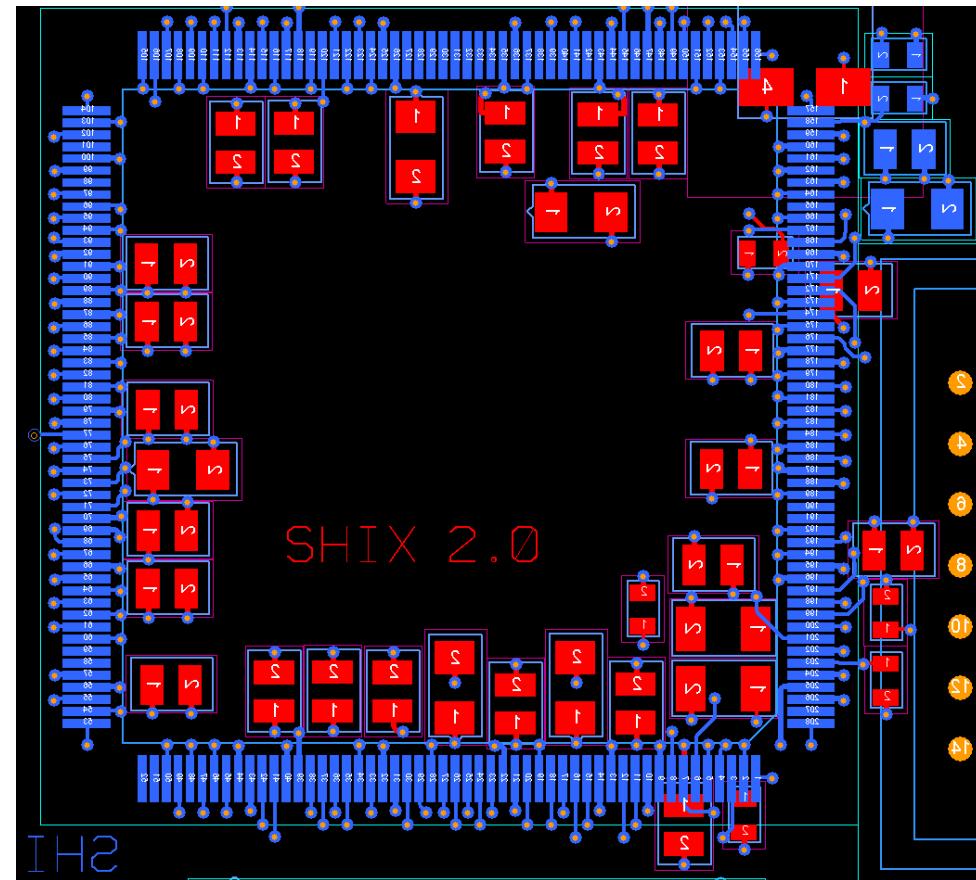

# PCB : CAO

## ● CAO PCB

- placement des composants

- manuel

- automatique

- swap

## ● Contraintes

- topologiques

- fonctionnalité

- fabrication (soudage)

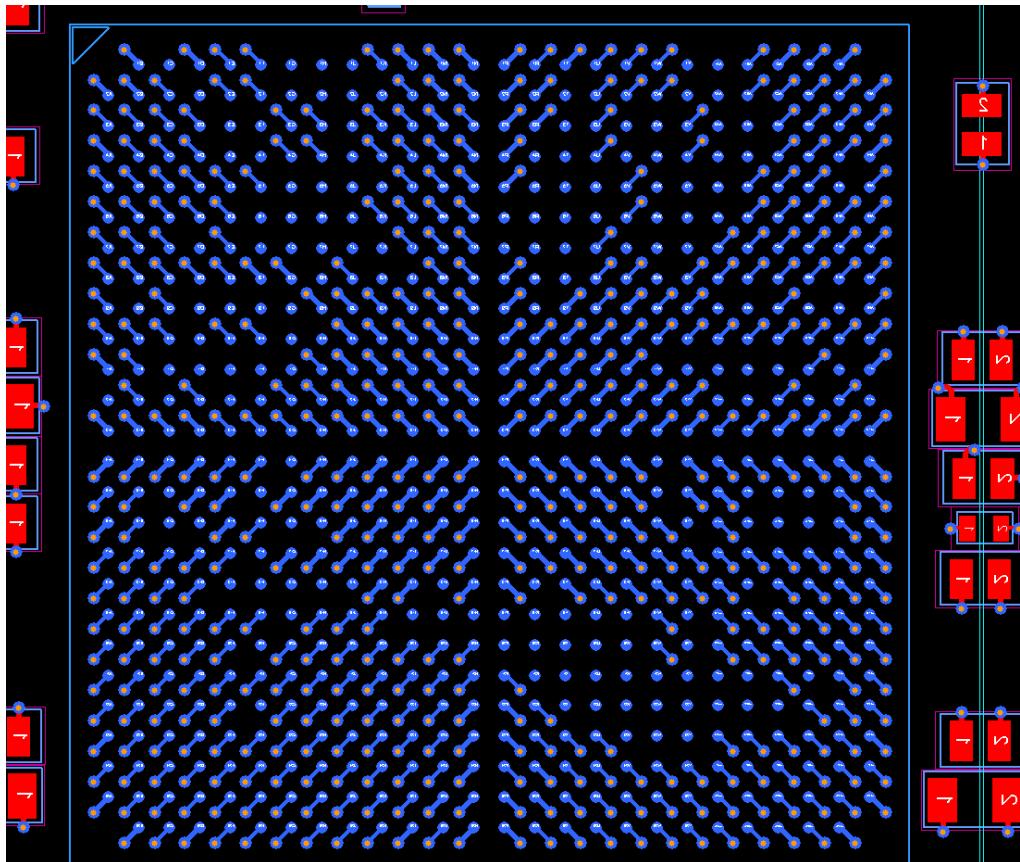

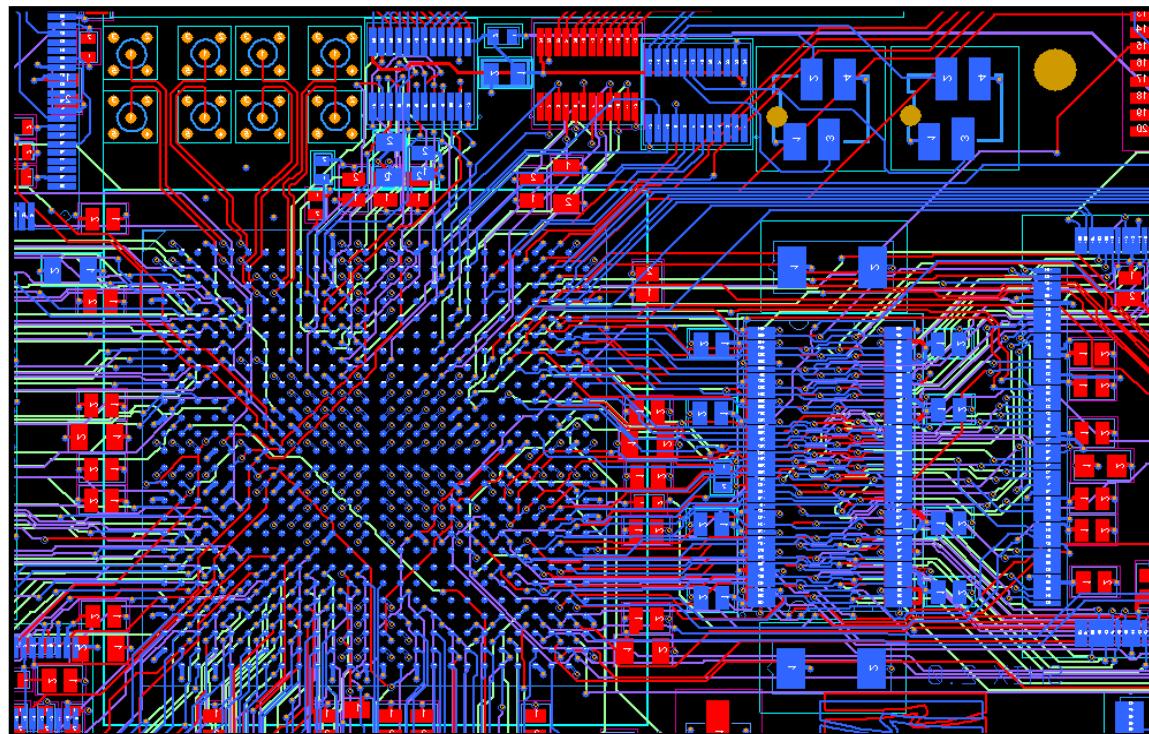

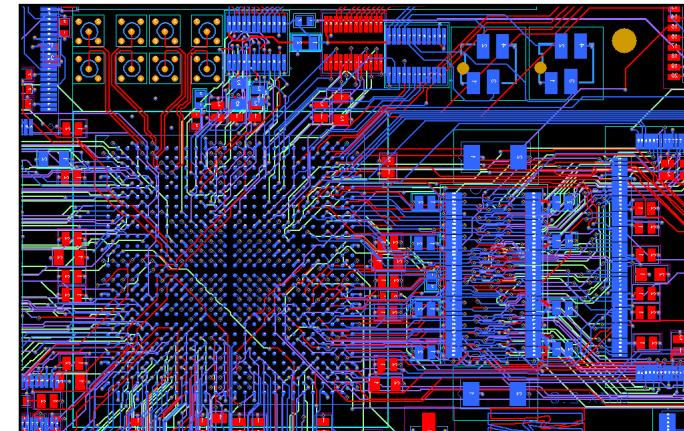

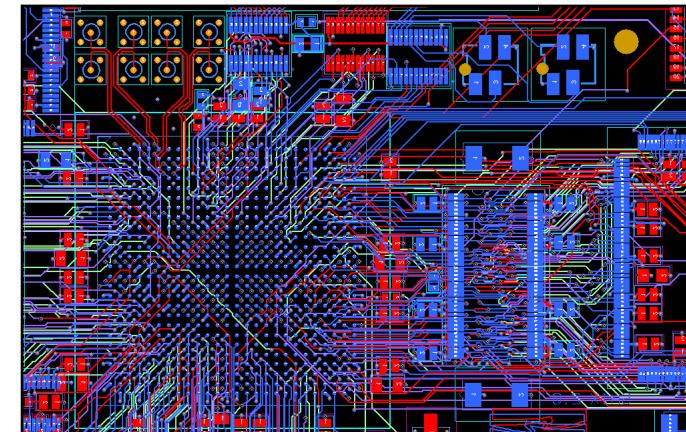

- CAO PCB

- fan out : sortie des composants

- CAO PCB

- routage des nets critiques

- routage des nets

### CAO PCB

- nets critiques

- horloges

- paires différentielles

- pistes analogiques

- pistes bruyantes (haute vitesse, fronts raides)

- routage

- manuel

- automatique (constraint)

- semi-automatique

- externe (intégrité du signal)

- attention, un routage beau n'est pas forcément la meilleure solution...

# CAO PCB

- simulations

- durant ou après le routage

- crosstalk, délais, overshoot, undershoot

- rétro annotation et bouclage éventuel

- finalisations

- angles

- teardrops, breakout

- points de test

- manuels

- automatiques

- grille / espace minimum grand

- il vaut mieux les prévoir tôt !

- suppression des antennes

## CAO PCB

- génération des plans

- positif / négatif

- suppression des îlots

- habillage

- mires / locating

- logos

- repérage des couches

- ...

## CAO PCB

- DRC / ERC

- Design Rules Check

- Electrical Rules Check

- Génération des fichiers de sorties

- GERBER

- DRILL

- rapports

- vérification, re-vérification,

- ...

### Montage :

- à piquer

- peut nécessiter un placement manuel

- encombrants : réservés aux fortes puissances (alimentations secteur) et aux connecteurs

- soudage manuel ou à la vague

- montés en surface : CMS (SMD)

- placement automatique

- sur une ou deux face(s)

- soudage à la vague ou en refusion

# PCB : les composants

## Soudage :

- à la vague :

- déplacement d'une vague d'étain en fusion sur le PCB, soudant au passage les composants exposés.

- contraintes :

- direction de la vague influe sur le placement et le sens des composants,

- hauteur des composants,

- espacements grands entre pastilles (ponts).

- refusion :

- dépôt de pâte à braser (nécessite un plan de « solder paste »)

- placement (et collage) des composants,

- chauffage de la carte.

- mixtes :

- refusion + vague

- double refusion

- double refusion + vague

### Conclusion :

- Phase critique : réalisation des bibliothèques.

- Les contraintes d'intégrité doivent être spécifiées en amont du design.

- Le routage doit pouvoir s'effectuer sous contraintes (process et IS)

- DRC / ERC

- online / batch

- Exemples de logiciels de CAO industriels :

- Expedition PCB (Mentor)

- Suite Allegro (Cadence)

**Le routage n'est plus du dessin : c'est une phase critique de la réalisation des systèmes électroniques (intégrité du signal)**