Institut

Mines-Télécom

# SoC-ELEC342

## Présentation

Tarik Graba

<tarik.graba@telecom-paristech.fr>

04 mai 2015

# Plan

## Les SoCs

Flot de développement

Objectifs de l'UE

Les outils utilisés

SocLib

SoC de base

Organisation

# Qu'est-ce qu'un SoC?

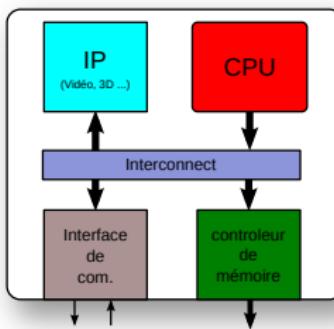

## SoC

Un SoC (System on Chip) est un circuit électronique **intégré** qui contient au moins un processeur et des blocs spécifiques pour l'aider à réaliser des tâches particulière.

# Qu'est-ce qu'un SoC?

## Pourquoi intégrer?

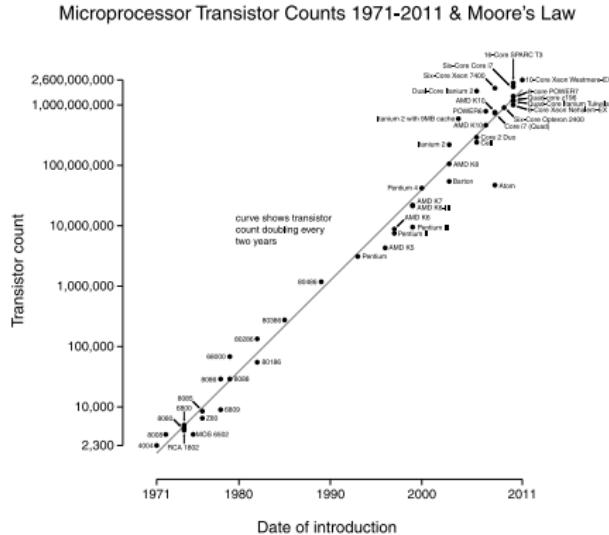

Parce qu'on la loi Moore nous le permet!

⇒ Doublement des densités d'intégration tous les 18/24 mois!

# Qu'est-ce qu'un SoC?

Pourquoi intégrer?

Parce que ça coute moins cher (en volume)

- Le prix est lié à la surface de la puce

- Moins de composants, PCB plus simple

- Couts d'assemblage

Parce que c'est plus performant

- Intégration

- Fréquences plus élevées

- Consommation réduite

- Moins de contraintes sur les PCB

# Qu'est-ce qu'un SoC?

## Où trouve-t-on des SoC?

- Dans les téléphones/ tablets

- Dans les TV, set-top box

- Dans les appareils photo

- Dans les imprimantes

- ...

## Qu'est-ce qu'un SoC?

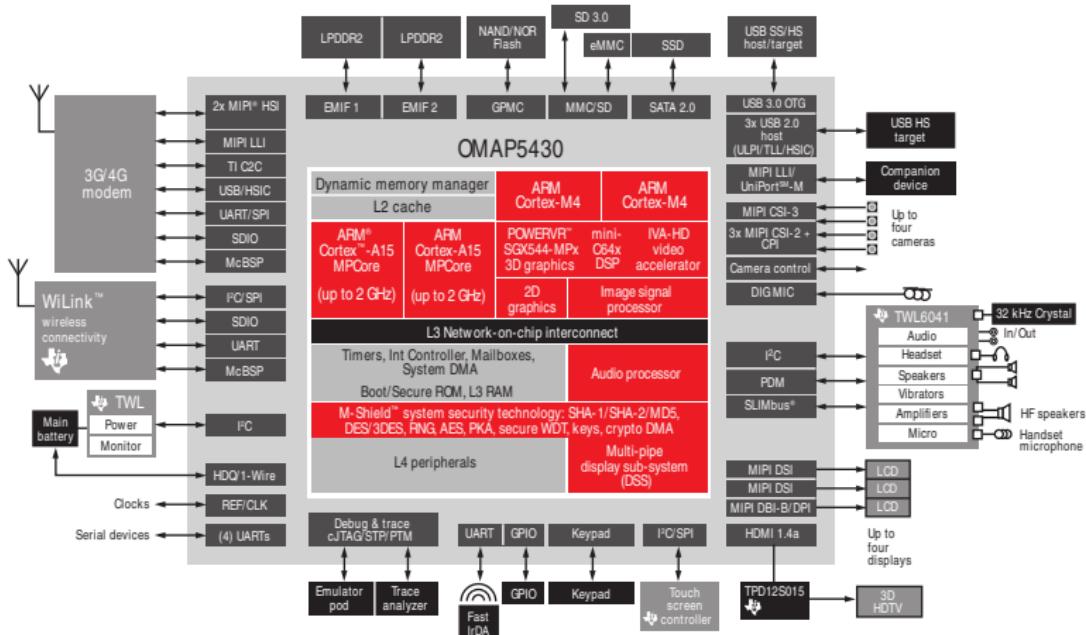

Exemple: OMAP5430 (Texas Instruments)

Source [http://focus.ti.com/pdfs/wtbu/OMAP5\\_2011-7-13.pdf](http://focus.ti.com/pdfs/wtbu/OMAP5_2011-7-13.pdf)

## Qu'est-ce qu'un SoC?

# Application Platform

- 2 Processeurs doubles cœurs (2 GHz)

- 1 DSP, Accélérateurs graphique, vidéo

- Ctrl DDR, IOs

- ...

[http://focus.ti.com/pdfs/wtbu/OMAP5\\_2011-7-13.pdf](http://focus.ti.com/pdfs/wtbu/OMAP5_2011-7-13.pdf)

# Qu'est-ce qu'un SoC?

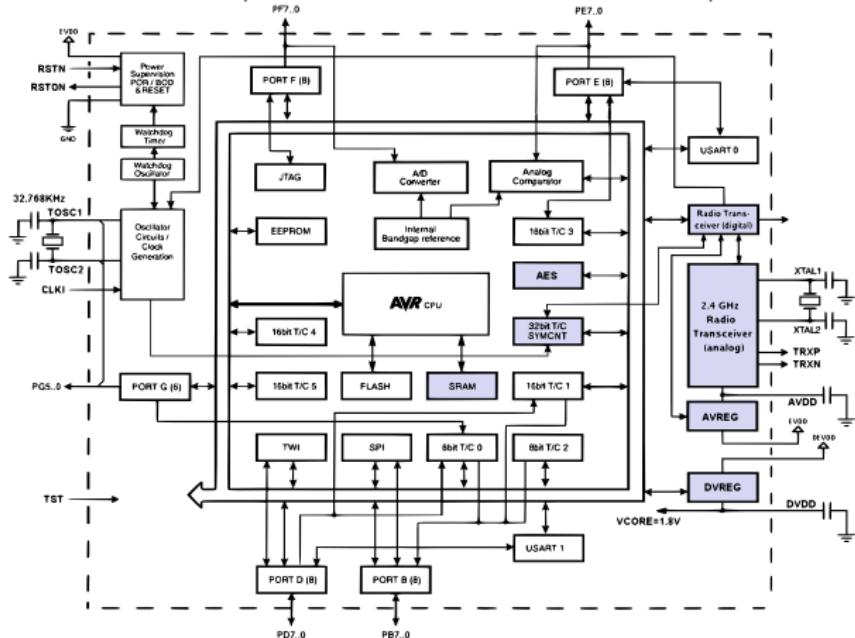

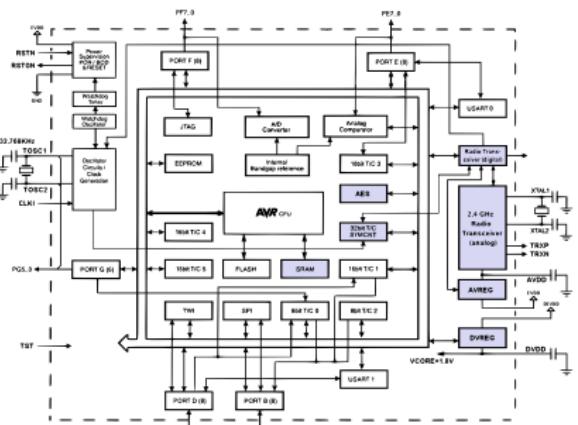

Exemple: AT32UC3A0128AU (Atmel)

Source <http://www.atmel.com/devices/ATMEGA128RFA1.aspx>

# Qu'est-ce qu'un SoC?

## Exemple: AT32UC3A0128AU (Atmel)

### Interface ZigBee

- 1 microcontrôleur 8bit (16 MHz)

- Transducteur IEEE 802.15.4

- ...

<http://www.atmel.com/devices/ATMEGA128RFA1.aspx>

# Qu'est-ce qu'un SoC?

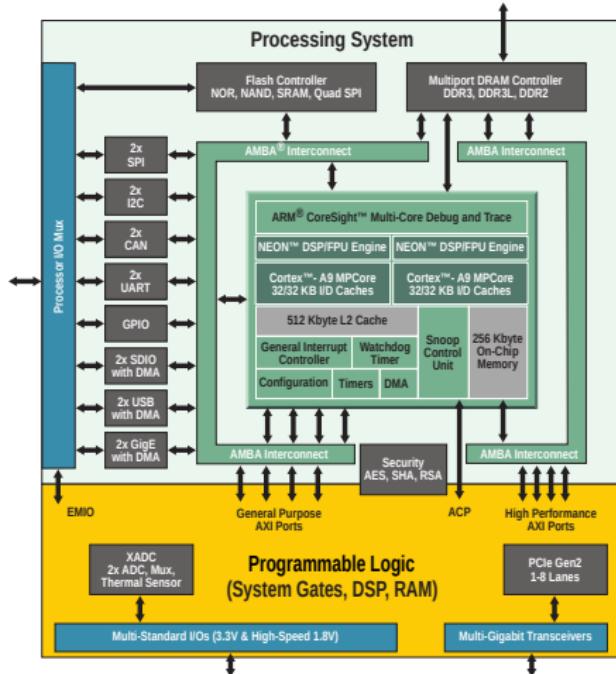

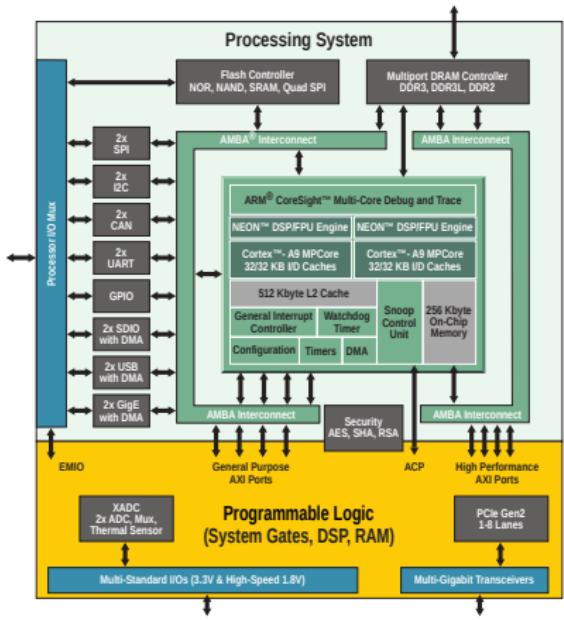

## Exemple: Zynq-7000 de Xilinx

Source <http://www.xilinx.com/content/xilinx/en/products/silicon-devices/soc/zynq-7000.html>

# Qu'est-ce qu'un SoC?

Exemple: Zynq-7000 de Xilinx

## SoC programmable

- Dual Cortex A9

- Matrice programmable (FPGA)

<http://www.xilinx.com/content/xilinx/en/products/silicon-devices/soc/zynq-7000.html>

# Qu'est-ce qu'un SoC?

## Du logiciel

- Ne pas réinventer la roue

- Systèmes d'exploitation

- Bibliothèques existantes

- GUI ...

- Le logiciel permet une évolution/adaptation plus simple

- On change le logiciel → on change l'application

- Corriger/contourner des Bugs!

# Qu'est-ce qu'un SoC?

## Du logiciel

### ■ Le maximum en soft

- Si c'est faisable avec un processeur existant on s'arrête là

- Le développement logiciel est plus simple/moins risqué économiquement

- Les clients vous le demanderons

# Qu'est-ce qu'un SoC?

## Du matériel

### ■ Les blocs appelés IPs (Intellectual Property)

- Des cœurs de processeurs

- Contrôleur de périphériques

- Accélérateur, coprocesseur

- ...

### ■ Comment?

- Les acheter (rapide/cher?)

- Les développer (long)

### ■ Réutiliser l'existant

# Qu'est-ce qu'un SoC?

## Du matériel

### ■ Pourquoi les rajoute-t-on?

- Pour répondre à des contraintes

- Le CPU va pas assez vite

- Le CPU consomme trop

- Le CPU est trop grand/coute trop cher

- On ne sais pas faire en logiciel

- Interfaces particulières

- Il faut aller vite

- Analogique!

# Qu'est-ce qu'un SoC?

## Exemple d'IPs

Quelles IPs sont disponibles?

- Des processeurs:

- ARM, Mips, 8051 ...

- Accélérateurs:

- OpenGL, vidéo, DSP ...

- Interfaces

- mémoires, USB, PCI, ...

- Infrastructure

- Bus, cache

# Qu'est-ce qu'un SoC?

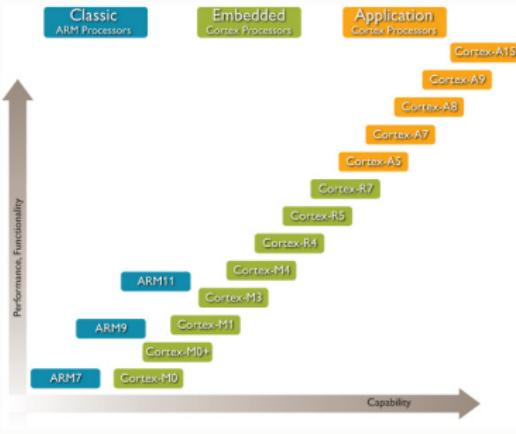

## Exemple de fournisseurs d'IPs: ARM

### Cœurs de CPU:

Source (2012)

<http://arm.com/products/processors/index.php>

- Des coeurs de CPU allant du microcontrôleur basse consommation au processeur applicatif haute performance.

- Infrastructure autour de ces processeurs (bus, cache, smp...)

- Développement de logiciel associé

- OS, compilateur, bibliothèques spécialisée

# Qu'est-ce qu'un SoC?

Exemple de fournisseurs d'IPs: Imagination Technologies

## Coprocesseurs graphiques

Source <http://www.imgtec.com>

### ■ Coprocesseurs graphiques

- OpenGL/OpenGL ES

- Codec vidéo ...

### ■ Logiciel support

- Drivers

- Bibliothèques

# Qu'est-ce qu'un SoC?

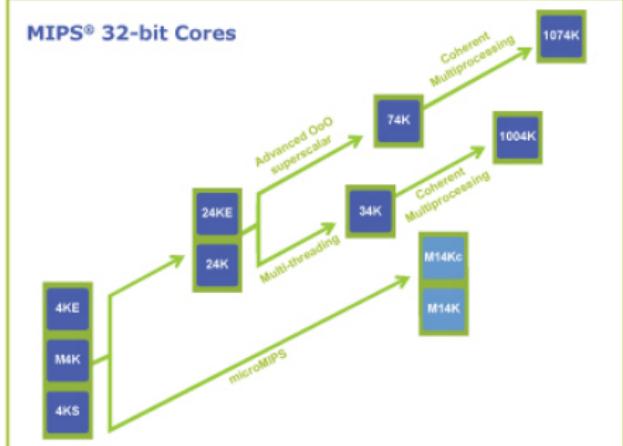

Exemple de fournisseurs d'IPs: MIPS

## Cœurs de CPU:

- Des coeurs de CPU 32 et 64bit

- Développement de logiciel associé

- OS, compilateur, bibliothèques spécialisée

- Maintenant propriété de Imagination Technologies

Source <http://mips.com/products/processor-cores>

# Qu'est-ce qu'un SoC?

Exemple de fournisseurs d'IPs

## Les fondeurs

- STMicroelectronics, Samsung, TSMC ...

## Les vendeur d'outils de CAO

- Cadence, Mentor, Synopsis

## Les autres

- Qui ne font que ça

...

# Qu'est-ce qu'un SoC?

## Résumons

Donc, pour concevoir un SoC il faut conjointement:

### ■ Concevoir du matériel

- Réutiliser des éléments existants (des IPs)

- Développer des éléments spécifiques nouveaux

### ■ Concevoir du logiciel

- Réutiliser des bibliothèques existantes

- Développer du code spécifique nouveau

- Interagir avec le matériel

### ■ Que l'ensemble respecte des contraintes de:

- temps réel, taille du circuit, consommation, délais, prix ...

# Plan

Les SoCs

Flot de développement

Objectifs de l'UE

Les outils utilisés

SocLib

SoC de base

Organisation

# Flot de développement

Passer de ça...

```

// 60 frames/s display

Thread1{

every(16.66 ms)

display(image)

}

// scene update

Thread2{

if(ViewChanged)

redraw(image)

}

// player interaction

Thread3{

wait(player1)

move(rabbit0)

}

```

...à ça!

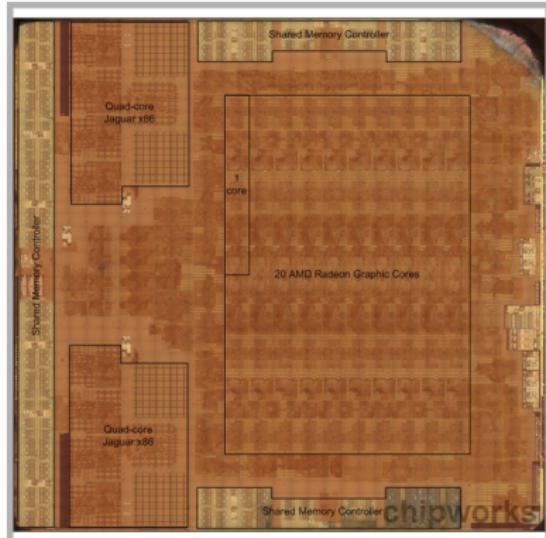

APU PS4 ( $18 \times 19\text{mm}^2$ ) TSMC 28-nm,

image <http://www.chipworks.com>

# Flot de développement

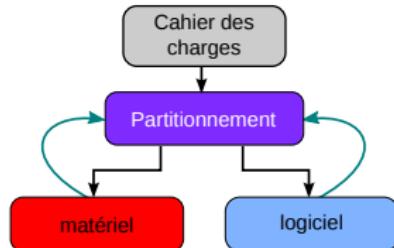

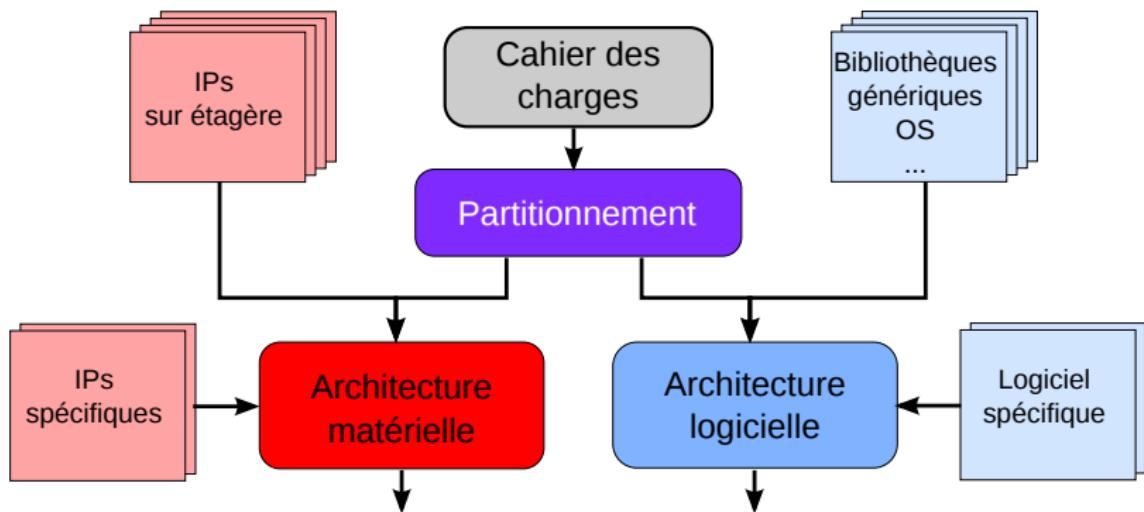

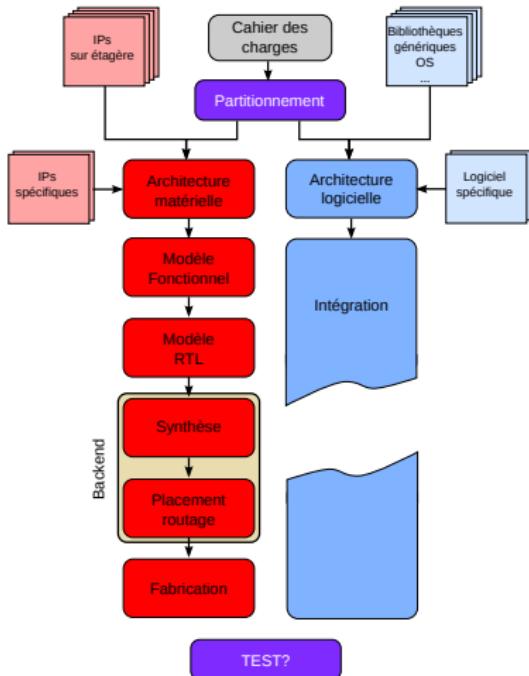

## Le partitionnement

A partir du cahier des charges vous devrez définir:

- Ce Qu'il faut faire:

- En logiciel

- En Matériel

# Flot de développement

## Le partitionnement

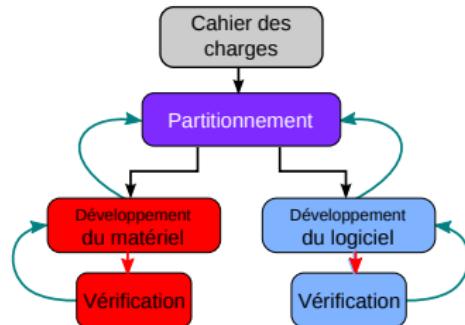

# Flot de développement

## Le développement

- Développement de logiciel/matériel

- Équipes différentes

- Rythmes différents

- Vérifications différentes

# Flot de développement

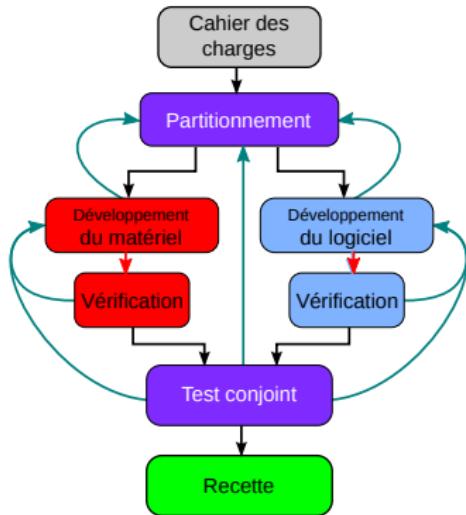

## La validation

- Valider le résultat de chaque flot par rapport à l'autre

# Flot de développement

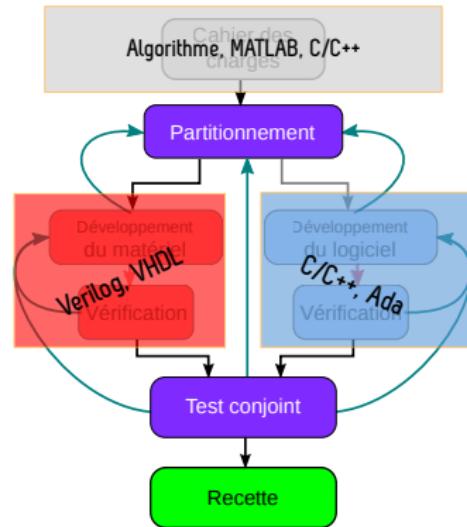

## La complexité

- Dans la vie réelle

- Équipes différentes

- Langages informatiques différents

- Philosophies différentes

# Flot de développement

## Les enjeux

# Flot de développement

## Les enjeux

- Commencer le développement du logiciel le plus tôt possible

- Comment faire avant que le matériel ne soit disponible?

- Garder un référentiel unique tout au long des phases de conception/vérification

# Flot de développement

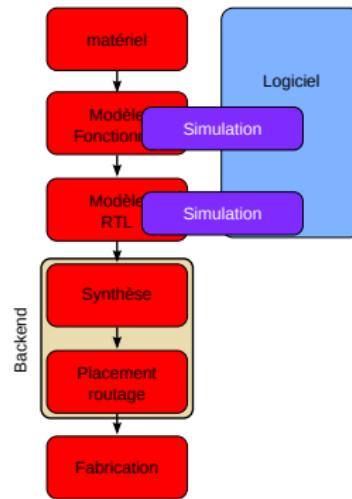

## La simulation

### La simulation

- Utiliser un modèle du matériel

- Quelle est la précision du modèle (cycle → transactionnel).

- Quelle est la vitesse de simulation.

- Utiliser le RTL

- En général très lent.

- Est-il disponible pour toutes les IPs?

- Il faut attendre qu'il soit prêt.

# Flot de développement

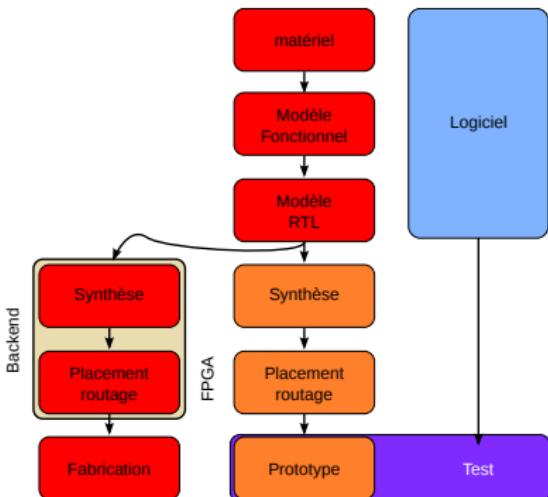

## Prototype FPGA

### Le prototype FPGA

#### ■ Le RTL doit être prêt

- Permet le test fonctionnel.

- Permet de valider le logiciel.

- Moins rapide que le circuit final.

#### ■ Le “backend” n'est pas celui de l'ASIC

- Bugs introduits par les outils de synthèse.

# Flot de développement

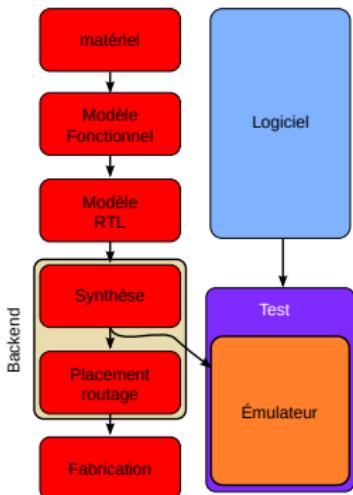

## L'émulation

## L'émulation

- Après la synthèse ASIC

- Utilise un émulateur

- Émule le résultat de la synthèse

- Utilise une batterie de FPGAs

- Beaucoup plus lent que le circuit final

- Principalement pour les tests de non régression

# Flot de développement

## L'émulation

<http://www.mentor.com/products/fv/emulation-systems>

### Exemple

#### ■ Veloce Quattro (Mentor Graphics)

- 8 à 128 Millions de portes

- 16MB à 256MB de mémoire embarquée

- Émulation de 1 à 1.5MHz

# Flot de développement

## Les plateformes virtuelles

### ■ Des plateformes virtuelles

- Simulation rapide (de quoi démarrer un OS)

- Modèles suffisamment précis (registres, irqs, ...)

- Interopérabilité (des standards comme SystemC TLM-2)

### ■ Qui permettent

- d'explorer des solutions architecturales

- d'estimer les performances

- de commencer à développer le logiciel

- de servir de modèle de référence

# Plan

Les SoCs

Flot de développement

Objectifs de l'UE

Les outils utilisés

SocLib

SoC de base

Organisation

# Objectifs de l'UE

## ■ Vous transmettre un savoir opérationnel

- Mise en oeuvre d'outils et de principes actuels

- Conception d'un SoC en utilisant des plateformes virtuelles

- Raffinement vers du RTL

- La synthèse et le placement routage (notions)

- Étude d'un cas réaliste (mais pas trop)

- Conception conjointe Logiciel/matériel

- Suffisamment simple pour finir (on l'espère)

- Si on va au bout on tentera le prototype sur FPGA

# Objectifs de l'UE

Important!!

- L'objectif principal est pédagogique

- Vous n'obtiendrez pas un SoC industriel

- Apprendre en étant confronté à une situation réaliste

- Nous n'avons de solution prête (encore)

- Nous n'avons pas fait le SoC avant vous

- Les outils que vous utiliserez ne sont pas magiques

- Sont parfois expérimentaux

- Ont parfois des bugs

- Sont parfois mal documentés

- Nous faisons partie de l'équipe comme vous...

# Plan

Les SoCs

Flot de développement

Objectifs de l'UE

Les outils utilisés

SocLib

SoC de base

Organisation

## ■ Bibliothèque d'IP pour la simulation de SoC

- Libre (distribuée sous licence GPL/LGPL)

- en SystemC (pas besoin de simulateur propriétaire)

- Pour chaque IP il existe un chemin vers la synthèse

## ■ IP disponibles

- Processeurs (sparc, mips, ...)

- RAM/ROM

- Terminal virtuel + uart

- interconnect

- On utilise seulement les éléments dont on a besoin

- On peut dimensionner certains éléments

- Taille des mémoires, des caches

- Latences de certains éléments

- etc ...

- On a accès au code (on peut éventuellement corriger des bugs!!)

- Certains utilitaires

- Charger les mémoires directement à partir d'un fichier elf

- Obtenir des statistiques sur le fonctionnement

# Le Processeur

## Le LM32

- LatticeMico32 (lattice Semiconductor)

- Processeur RISC 32bits, 6 étages de pipeline

- 32 registres généraux

- Configurable (destiné aux FPGAs)

- multiplicateur, diviseur, registre à décalage

- caches données et instructions séparées

- interface wishbone

- Description RTL disponible librement (Verilog)

- Modèle disponible dans SocLib

# Le Processeur

## Le LM32

### ■ Chaine de développement GNU:

- gcc 4.5.4 (preprocesor, compiler ...)

- binutils 2.22 (assembler, linker, ...)

- gdb 7.7 (debugger)

- voir [/comelec/softs/opt/gnu\\_tools\\_for\\_lm32](/comelec/softs/opt/gnu_tools_for_lm32)

### ■ Ports d'OS existent:

- uCLinux (pas de mmu)

- uCosII, freeRTOS ...

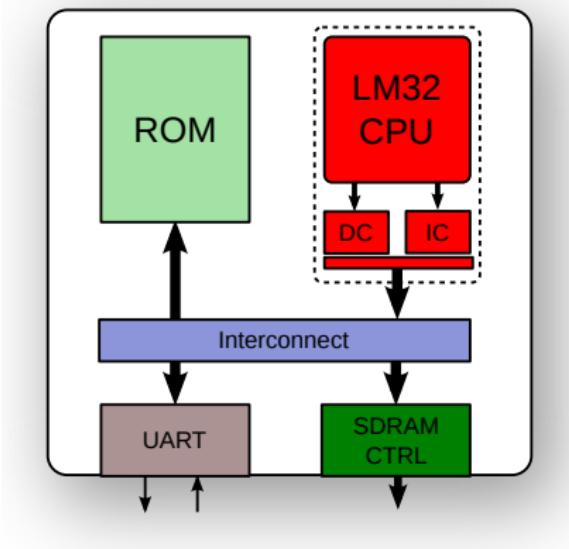

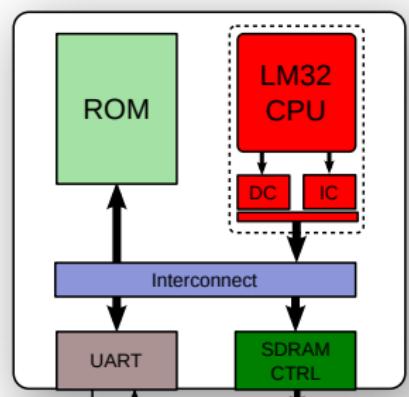

# System de Base

## SoC à base de LM32

# System de Base

## SoC à base de LM32

On démarrera avec un SoC de base:

- Un processeur

- LM32

- Caches

- données/instructions

- Un interconnect

- Wishbone

- Arbitre

- Des IPs

- Une ROM

- Un contrôleur pour SDRAM

- Une UART

# Les IPs

## Autres

### ■ La ROM

- Contiendra le programme au démarrage du système

### ■ Contrôleur mémoire SDRAM

- Les SDRAM seront des éléments extérieurs au SoC

- La mémoire embarquée est limitée

### ■ UART

- Pour communiquer éventuellement avec l'extérieur

### ■ Un bus

- L'interface Wishbone

- Un arbitre permettant d'avoir plusieurs maîtres

# Plan

Les SoCs

Flot de développement

Objectifs de l'UE

Les outils utilisés

SocLib

SoC de base

Organisation

# Le planning

---

|              |       |                                                           |

|--------------|-------|-----------------------------------------------------------|

| Introduction |       | Ce que l'on fait actuellement                             |

| Architecture | 4 TH  | Définition de l'architecture                              |

| Modélisation | 16 TH | Modélisation haut niveau du SoC en SystemC                |

| RTL          | 12 TH | Raffinement du modèle SystemC en modèle RTL synthétisable |

| Backend      | 3 TH  | Synthèse ASIC et placement routage du SoC                 |

| Recette      | 1 TH  | Présentation finale de vos travaux                        |

---

# Organisation du travail

- Tous les enseignements se feront en salle info.

- Encadrants:

- Sumanta Chaudhuri

- Tarik Graba

- Yves Mathieu

- Vous travaillerez en équipes:

- 3 personnes

- Partage du travail

# L'évaluation

- Vous tiendrez à jour un journal

- Qu'est ce que nous avons fait?

- Pourquoi?

- Comment?

- Quels résultats?

- Régulièrement vous présenterez brièvement l'état d'avancement de votre travail

- Vous serez notés par équipes

- Si le produit n'est pas livré toute l'équipe est licenciée

- Chaque responsable est noté sur la réalisation de sa tâche

- Vous serez aussi notés individuellement

- Des exposés, peut-être