PROCESSEURS ET ARCHITECTURES

NUMÉRIQUES (PAN)

SUPPORT DE COURS

ANNÉE 2018/2019

SUMANTA CHAUDHURI

JEAN-LUC DANGER

GUILLAUME DUC

TARIK GRABA

ULRICH KÜHNE

YVES MATHIEU

ALEXIS POLTI

LAURENT SAUVAGE

# Table des matières

|     |                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------|----|

| 1   | <i>De la logique combinatoire à l'arithmétique</i>                                        | 5  |

| 1.1 | <i>La logique booléenne</i>                                                               | 5  |

| 1.2 | <i>Fonctions logiques élémentaires</i>                                                    | 7  |

| 1.3 | <i>Fonctions logiques importantes</i>                                                     | 10 |

| 1.4 | <i>Représentation des nombres</i>                                                         | 14 |

| 1.5 | <i>Opérateurs arithmétiques</i>                                                           | 18 |

| 1.6 | <i>Du temps de propagation au temps de calcul</i>                                         | 22 |

| 2   | <i>La logique séquentielle</i>                                                            | 25 |

| 2.1 | <i>Mémorisation et logique séquentielle</i>                                               | 25 |

| 2.2 | <i>Logique séquentielle synchrone</i>                                                     | 25 |

| 2.3 | <i>La bascule D</i>                                                                       | 27 |

| 2.4 | <i>Généralisation</i>                                                                     | 33 |

| 2.5 | <i>Applications de la logique synchrone</i>                                               | 35 |

| 3   | <i>Les unités de contrôle</i>                                                             | 41 |

| 3.1 | <i>Automates matériels synchrones</i>                                                     | 41 |

| 3.2 | <i>Codage SystemVerilog des automates</i>                                                 | 43 |

| 4   | <i>Le nano processeur</i>                                                                 | 47 |

| 4.1 | <i>Programme, instructions et données</i>                                                 | 47 |

| 4.2 | <i>La mémoire RAM</i>                                                                     | 48 |

| 4.3 | <i>Le système de base</i>                                                                 | 50 |

| 4.4 | <i>Première version du microprocesseur : l'automate linéaire</i>                          | 51 |

| 4.5 | <i>Deuxième version du microprocesseur : l'automate avec accumulateur</i>                 | 56 |

| 4.6 | <i>Troisième version du microprocesseur : l'automate avec accumulateur et indirection</i> | 60 |

| 4.7 | <i>Quatrième version du microprocesseur : le processeur RISC</i>                          | 64 |

| 4.8 | <i>Les périphériques</i>                                                                  | 69 |

|     |                                                                                            |     |

|-----|--------------------------------------------------------------------------------------------|-----|

| 5   | <i>La logique CMOS</i>                                                                     | 71  |

| 5.1 | <i>Construisons des fonctions logiques</i>                                                 | 71  |

| 5.2 | <i>La logique CMOS</i>                                                                     | 73  |

| 5.3 | <i>Performances de la logique CMOS</i>                                                     | 75  |

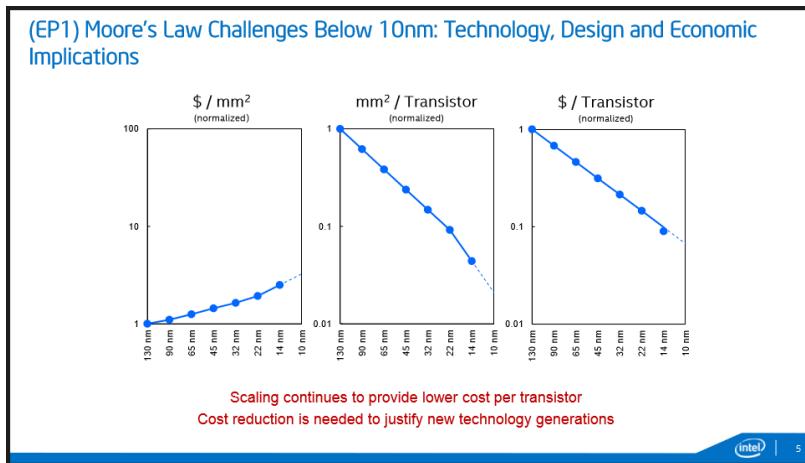

| 5.4 | <i>Évolutions technologiques et lois de Moore</i>                                          | 79  |

| A   | <i>Annexe : SystemVerilog</i>                                                              | 87  |

| A.1 | <i>Quelques règles générales de syntaxe</i>                                                | 87  |

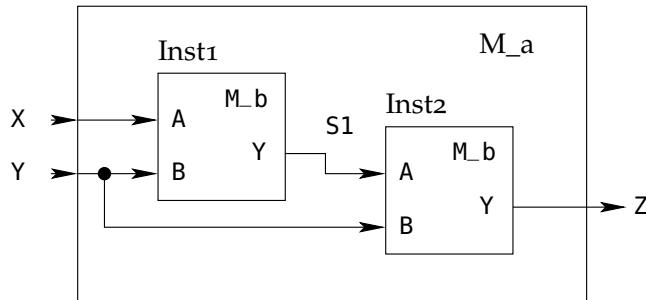

| A.2 | <i>Les modules</i>                                                                         | 87  |

| A.3 | <i>Contenu des modules : Structures et instantiation de modules</i>                        | 89  |

| A.4 | <i>Contenu des modules : Description d'un comportement combinatoire</i>                    | 90  |

| A.5 | <i>Contenu des modules : Description d'un comportement séquentiel synchrone</i>            | 95  |

| A.6 | <i>Généralisation des processus <b>always</b></i>                                          | 97  |

| A.7 | <i>Codage des états des automates finis</i>                                                | 98  |

| B   | <i>Annexe : Sujets de travaux dirigés</i>                                                  | 101 |

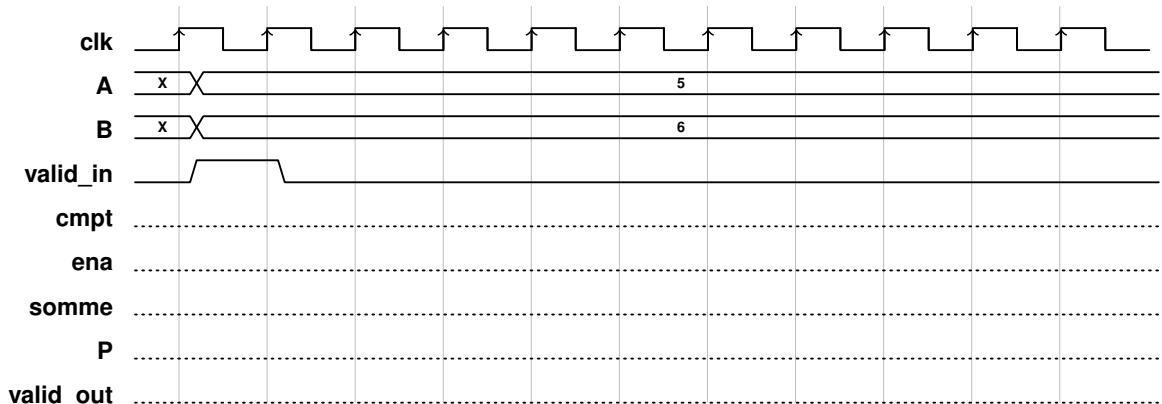

| B.1 | <i>TD1 : Logique séquentielle synchrone</i>                                                | 101 |

| B.2 | <i>TD2 : Représentation des nombres, opérateurs de calcul séquentiels et combinatoires</i> | 103 |

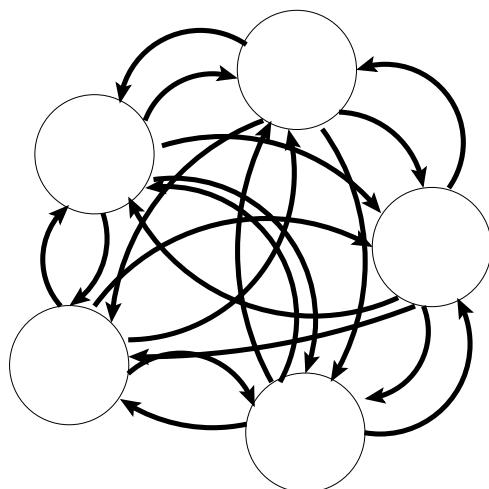

| B.3 | <i>TD3 : Automates matériels</i>                                                           | 106 |

| C   | <i>Annexe : Exemples de constructions synchrones</i>                                       | 111 |

| C.1 | <i>Les bascules</i>                                                                        | 111 |

| C.2 | <i>Les compteurs</i>                                                                       | 112 |

| C.3 | <i>Détecteur de fronts montants</i>                                                        | 117 |

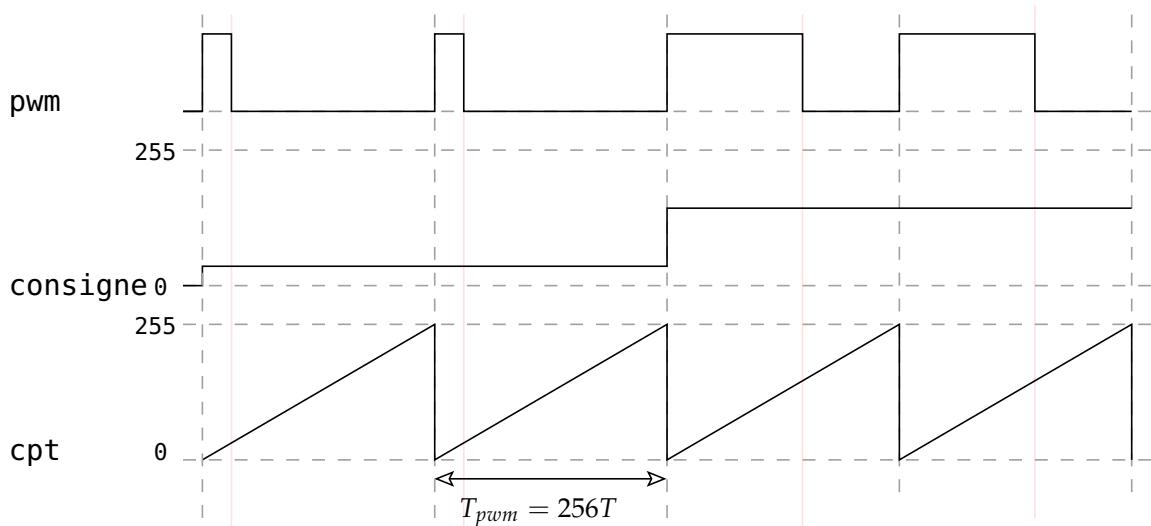

| C.4 | <i>PWM : Pulse Width Modulation</i>                                                        | 119 |

# 1

## *De la logique combinatoire à l'arithmétique*

*Dans ce chapitre, nous allons introduire la notion de logique combinatoire en présentant les bases de la logique booléenne (cf. section 1.1), puis les fonctions logiques élémentaires (cf. section 1.2) ainsi quelques fonctions plus complexes mais souvent utilisées (cf. section 1.3). Nous verrons ensuite comment représenter des nombres (cf. section 1.4) et comment réaliser des opérations sur ces nombres (cf. section 1.5). Enfin, nous introduirons le concept de temps de propagation dans les opérateurs logiques (cf. section 1.6).*

### *1.1 La logique booléenne*

#### *1.1.1 Introduction*

Soit  $E$  l'ensemble à deux éléments 0, 1.

Une *variable logique* est un élément de  $E$ . Elle ne possède donc que deux états : 0 ou 1.

Une *fonction logique* est une application de  $E \times E \dots \times E$  dans  $E$  qui associe à un  $n$ -uplet de variables logiques  $(e_0, e_1, \dots, e_n)$ , souvent appelées *entrées*, une variable logique  $s = F(e_0, e_1, \dots, e_n)$ , souvent appelée *sortie*.

On distingue deux catégories de fonctions logiques, en fonction de leur comportement temporel.

Une *fonction combinatoire* est une fonction logique pour laquelle la sortie ne dépend que de l'état actuel des entrées :

$$\forall t, s(t) = F(e_0(t), e_1(t), \dots, e_n(t))$$

Une *fonction séquentielle* est une fonction logique pour laquelle la sortie dépend de l'état actuel de ses entrées mais également de leurs états passés :

$$s(t) = F(e_0(t), e_1(t), \dots, e_n(t), e_0(t - t_1), e_1(t - t_1) \dots)$$

Dans ce chapitre, nous ne traiterons que des fonctions combinatoires. Les fonctions séquentielles seront introduites dans le chapitre 2.

#### *1.1.2 Représentation des fonctions logiques*

Il existe plusieurs méthodes pour décrire une fonction logique combinatoire. Ces méthodes sont toutes équivalentes et le choix de l'une ou l'autre ne va dépendre que du contexte d'utilisation.

*Table de vérité* La première méthode consiste à lister, pour chacune des valeurs possibles de ses entrées, la valeur de la sortie de la fonction. Cette liste, présentée très souvent sous forme de table, est appelée *table de vérité*.

L'inconvénient majeur de cette méthode est que cette table peut être très grande. En effet, si la fonction prend en entrée  $N$  variables logiques, il faut  $2^N$  lignes dans cette table pour lister l'ensemble des valeurs possibles des entrées.

Exemple d'une table de vérité d'une fonction prenant en entrée deux variables logiques  $a$  et  $b$  :

| $a$ | $b$ | $s$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

TABLE 1.1: Exemple d'une fonction prenant en entrée deux variables logiques  $a$  et  $b$

*Équation analytique* Cette méthode consiste à donner l'équation de la sortie de la fonction en fonction de ses entrées. La liste et la signification des opérateurs seront données dans la section sur les fonctions logiques de base.

Exemple d'une fonction prenant en entrée trois variables logiques  $a$ ,  $b$  et  $c$  :  $s = a \cdot b + \bar{c}$ .

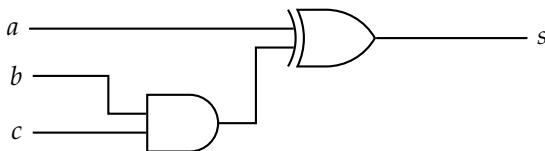

*Représentation schématique graphique* Cette méthode consiste à représenter graphiquement une fonction booléenne à l'aide à l'aide du schéma normalisé<sup>1</sup> des fonctions de base et de traits servant à indiquer la "connexion" d'une sortie à une entrée.

*Description fonctionnelle* Cette méthode consiste à décrire, en langage naturel, le comportement de la sortie en fonction des entrées de la fonction.

Exemple : la sortie  $s$  vaut 1 si, et seulement si, au moins une des entrées  $a$  ou  $b$  vaut 1.

1. Il existe plusieurs normes pour représenter ces fonctions de base. Dans ce cours, nous utiliserons la norme "américaine" (issue de ANSI 91-1984) car c'est l'une des plus utilisées. Il existe également une norme "européenne" (IEC 60617-12).

*Langage de description de matériel* Cette méthode consiste à décrire la fonction dans un langage particulier, appelé *langage de description de matériel* (*Hardware Description Language* — HDL), facilement compréhensible par un ordinateur. Il en existe plusieurs et dans ce cours nous utiliserons SystemVerilog.

Ce langage sera introduit tout au long de ce cours et une synthèse est présentée page 87.

Exemple :

---

```

logic A, B, C, S;

always@(*)

S <= A ^ B | C;

```

---

## 1.2 Fonctions logiques élémentaires

Cette section présente les fonctions logiques élémentaires, également appelées *portes logiques*, couramment utilisées par la suite.

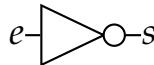

### 1.2.1 L'inverseur (NOT)

#### Description

La sortie vaut 1 si, et seulement si, l'entrée vaut 0.

| Table de vérité | Équation | Symbole |

|-----------------|----------|---------|

|-----------------|----------|---------|

| e | s |

|---|---|

| 0 | 1 |

| 1 | 0 |

Description en SystemVerilog

---

```

logic s, e;

always@(*)

s <= ~e;

```

---

Explications :

- La première ligne permet de déclarer deux *signaux* (de type `logic` donc sur 1 bit), nommés `s` et `e`

- La deuxième ligne indique que ce qui suit (donc la troisième ligne) doit être ré-évalué dès que nécessaire (dans notre cas, dès que `e` va changer, ce qui correspond bien à un comportement combinatoire)

- `<=` est l'opérateur d'affectation (c'est-à-dire que la valeur située à droite de cet opérateur est affectée au signal situé à gauche de l'opérateur)

- `~` est l'opérateur unaire d'inversion bit-à-bit (donc notre opérateur NON)

- La troisième ligne indique donc qu'il faut affecter au signal `s` le complément de la valeur du signal `e`

### 1.2.2 Le ET (AND)

#### Description

La sortie vaut 1 si, et seulement si, les deux entrées valent 1.<sup>2</sup>

| Table de vérité | Équation | Symbole |

|-----------------|----------|---------|

|-----------------|----------|---------|

| a | b | s |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2. La fonction ET peut être aussi interprétée comme une fonction de forçage à zéro d'un signal : dans l'expression  $s = valid \cdot b$ , le signal `s` ne vaut `b` que si `valid = 1` sinon il vaut 0.

Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= a & b;

```

---

En SystemVerilog, & représente l'opérateur ET bit-à-bit.

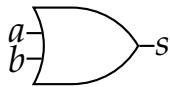

#### 1.2.3 Le OU (OR)

Description

La sortie vaut 0 si, et seulement si, les deux entrées valent 0.<sup>3</sup>

Table de vérité

Équation

Symbole

| a | b | s |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$$s = a + b$$

3. La fonction OU peut être aussi interprétée comme une fonction de forçage à un d'un signal : dans l'expression  $s = \text{force} + b$ , le signal  $s$  ne vaut  $b$  que si  $\text{force} = 0$  sinon il vaut 1.

Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= a | b;

```

---

En SystemVerilog, | représente l'opérateur OU bit-à-bit.

#### 1.2.4 Le NON ET (NAND)

Table de vérité

Description

Il s'agit de la fonction complémentaire du ET.

La sortie vaut 0 si, et seulement si, les deux entrées valent 1.

Table de vérité

Équation

| a | b | s |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$s = \overline{a \cdot b}$$

Symbole

Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= ~(a & b);

```

---

### 1.2.5 Le NON OU (NOR)

#### Description

Il s'agit de la fonction complémentaire du OU.

La sortie vaut 1 si, et seulement si, les deux entrées valent 0.

Table de vérité

Équation

| a | b | s |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

#### Symbole

#### Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= ~(a | b);

```

---

### 1.2.6 Le OU exclusif (XOR)

#### Description

La sortie vaut 1 si une, et seulement une, des deux entrées vaut 1.

4. La fonction OU exclusif peut être aussi interprétée comme une fonction de sélection entre une donnée et son complémentaire : dans l'expression  $s = selcomp \oplus b$ , le signal  $s$  ne vaut  $b$  que si  $selcomp = 0$  sinon il vaut  $\bar{b}$

Table de vérité

Équation

Symbol

| a | b | s |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$s = a \oplus b$

$= a \cdot \bar{b} + \bar{a} \cdot b$

#### Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= a ^ b;

```

---

En SystemVerilog,  $^$  représente l'opérateur OU exclusif bit-à-bit.

### 1.2.7 Le NON OU exclusif (XNOR)

#### Description

Il s'agit de la fonction complémentaire du OU exclusif. La sortie vaut 1 si, et seulement si, les deux entrées sont égales.

Table de vérité

| $a$ | $b$ | $s$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

Équation

$$s = \overline{a \oplus b}$$

$$= a \cdot b + \overline{a} \cdot \overline{b}$$

#### Symbole

#### Description en SystemVerilog

---

```

logic s, a, b;

always@(*)

s <= ~(a ^ b);

```

---

## 1.3 Fonctions logiques importantes

Les fonctions logiques élémentaires vues précédemment dans la section 1.2 permettent de construire toutes les fonctions logiques combinatoires. Dans cette section, nous présenterons quelques fonctions logiques un peu plus élaborées couramment utilisées.

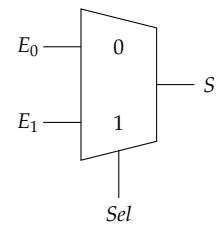

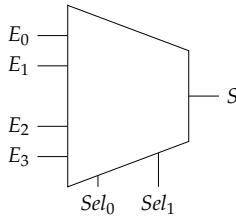

### 1.3.1 Le multiplexeur

Un multiplexeur<sup>5</sup> à  $N$  entrées, est une fonction logique dont la sortie est égale à l'une de ses  $N$  entrées. Le choix parmi les  $N$  entrées se fait grâce à une entrée particulière de sélection.

*Multiplexeur à deux entrées* Le multiplexeur le plus simple est le multiplexeur à deux entrées, dont le schéma est le suivant :

Si l'entrée  $Sel$  vaut 0, la sortie  $S$  du multiplexeur vaudra la valeur présente sur l'entrée  $E_0$ . De même, si  $Sel$  vaut 1, la sortie  $S$  vaudra la valeur présente sur l'entrée  $E_1$ .

La table de vérité du multiplexeur à deux entrées est la suivante :

5. Parfois appelé également fonction d'aiguillage

| Sel | $E_1$ | $E_0$ | $S$ |

|-----|-------|-------|-----|

| 0   | 0     | 0     | 0   |

| 0   | 0     | 1     | 1   |

| 0   | 1     | 0     | 0   |

| 0   | 1     | 1     | 1   |

| 1   | 0     | 0     | 0   |

| 1   | 0     | 1     | 0   |

| 1   | 1     | 0     | 1   |

| 1   | 1     | 1     | 1   |

Le comportement de ce multiplexeur peut également être décrit par l'équation suivante :

$$S = Sel \cdot E_1 + \overline{Sel} \cdot E_0$$

Enfin, il peut également être décrit de plusieurs manières en SystemVerilog :

---

```

logic S, Sel, E0, E1;

always@(*)

S <= (Sel & E1) | (~Sel & E0);

```

---

Le code précédent est une simple transcription de l'équation analytique du multiplexeur. Il existe cependant d'autres constructions, plus proches des langages informatiques classiques, qui permettent également de décrire le comportement du multiplexeur.

---

```

logic S, Sel, E0, E1;

always@(*)

if (Sel) S <= E1;

else S <= E0;

```

---

La construction `if...else` fonctionne comme dans les langages informatiques classiques. La condition du test est située entre parenthèses juste après le `if` et doit être une expression renvoyant vrai ou faux. En SystemVerilog, un signal (ici `Sel`) valant 1 est considéré comme vrai (dans ce cas la branche principale du `if` est prise) et un signal valant 0 est considéré comme faux (dans ce cas la branche `else` est prise).

---

```

logic S, Sel, E0, E1;

always@(*)

case(Sel)

1'b0: S <= E0;

1'b1: S <= E1;

endcase

```

---

La construction `case...endcase`<sup>6</sup> permet de tester simplement les différentes valeurs<sup>7</sup> possibles de la condition (ici `Sel`) sans avoir à imbriquer de nombreux `if...else`.

6. N'oubliez pas le `endcase`.

7. La construction `1'b0` est décrite en détail page 16. Ici, `1'b0` représente la valeur logique 0 et `1'b1` représente la valeur logique 1.

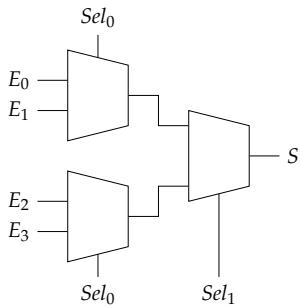

*Multiplexeur à  $n$  entrées* On peut généraliser et disposer de multiplexeurs à  $2^N$  entrées. Dans ce cas, il faut  $N$  entrées de sélection afin de pouvoir choisir une parmi les  $2^N$  entrées.

Exemple, le multiplexeur à 4 entrées :

dont l'équation est :

$$S = \overline{Sel_1} \cdot \overline{Sel_0} \cdot E_0 + \overline{Sel_1} \cdot Sel_0 \cdot E_1 + Sel_1 \cdot \overline{Sel_0} \cdot E_2 + Sel_0 \cdot Sel_1 \cdot E_3$$

Ce multiplexeur peut être réalisé grâce à trois multiplexeurs à 2 entrées :

### 1.3.2 Le décodeur

Un décodeur est une fonction logique à  $N$  entrées et  $2^N$  sorties<sup>8</sup> dont une, et une seule, sortie vaut 1, le numéro de cette sortie active étant la valeur présente sur l'entrée, considérée comme un nombre entier codé sur  $N$  bits (voir section 1.4.1 sur la représentation des nombres entiers).

*Exemple : Décodeur 2 vers 4* La table de vérité du décodeur 2 vers 4 est la suivante :

| $E_1$ | $E_0$ | $S_0$ | $S_1$ | $S_2$ | $S_3$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 1     | 0     | 0     | 0     |

| 0     | 1     | 0     | 1     | 0     | 0     |

| 1     | 0     | 0     | 0     | 1     | 0     |

| 1     | 1     | 0     | 0     | 0     | 1     |

Les équations logiques des sorties sont les suivantes :

$$S_0 = \overline{E_0} \cdot \overline{E_1}$$

$$S_1 = E_0 \cdot \overline{E_1}$$

$$S_2 = \overline{E_0} \cdot E_1$$

$$S_3 = E_0 \cdot E_1$$

De même que pour le multiplexeur, il existe plusieurs manières pour décrire le décodeur en SystemVerilog :

8. On utilise également la terminologie décodeur  $N$  vers  $2^N$ , exemple : décodeur 2 vers 4

---

```

logic E0, E1, S0, S1, S2, S3, S4;

always@(*)

begin

S0 <= ~E0 & ~E1;

S1 <= E0 & ~E1;

S2 <= ~E0 & E1;

S3 <= E0 & E1;

end

```

---

Il s'agit ici simplement d'une transcription directe des équations décrivant les sorties en fonction des entrées. Notez ici l'utilisation de la construction `begin...end` nécessaire lorsque plusieurs opérations (affectation, `if...else`, `case...endcase`, etc.) sont décrites au sein du même bloc `always`.

---

```

logic S0, S1, S2, S3, S4;

logic [1:0] E;

always@(*)

begin

S0 <= 1'b0;

S1 <= 1'b0;

S2 <= 1'b0;

S3 <= 1'b0;

if (E == 2'b00) S0 <= 1'b1;

if (E == 2'b01) S1 <= 1'b1;

if (E == 2'b10) S2 <= 1'b1;

if (E == 2'b11) S3 <= 1'b1;

end

```

---

Ce code introduit plusieurs nouvelles notions en SystemVerilog :

- `logic [1:0] E` déclare un vecteur de deux bits. Le premier nombre entre crochet (ici 1) indique l'indice du bit de poids fort<sup>9</sup> dans le vecteur et le second nombre (ici 0) indique l'indice du bit de poids faible. La dimension en bits du vecteur est donc la différence entre ces deux nombres plus un (donc ici  $1 - 0 + 1 = 2$ ). On peut accéder à la valeur d'un des bits du vecteur à l'aide de l'opérateur `[]` (donc ici `E[1]` est le bit de poids fort et `E[0]` le bit de poids faible).

- Un vecteur de bits (comme `E`), peut être comparé avec un nombre. Le contenu du vecteur est alors considéré comme un nombre entier représenté en binaire.

- Dans un bloc `always`, si plusieurs valeurs sont affectées à un même signal, la dernière (dans l'ordre d'écriture du code) "gagne". Cette propriété est utilisée ici pour affecter 0 par défaut aux sorties, sauf si elles sont concernées par la suite par un des `if`.

9. La définition de bit de poids fort/faible est donnée plus loin dans la section 1.4.1

---

```

logic S0, S1, S2, S3, S4;

logic [1:0] E;

```

```

always@(*)

begin

S0 <= 1'b0;

S1 <= 1'b0;

S2 <= 1'b0;

S3 <= 1'b0;

case (E)

2'b00: S0 <= 1'b1;

2'b01: S1 <= 1'b1;

2'b10: S2 <= 1'b1;

default: S3 <= 1'b1; // Correspond au cas E==2'b11

endcase

end

```

---

Dans cet exemple, les `if` précédents sont remplacés par une construction `case...endcase`. Le mot clé `default` permet de définir la branche du `case` prise dans le cas où aucune autre ne l'est. Afin d'éviter des constructions qui ne décriraient pas de la logique combinatoire, il est recommandé de toujours spécifier une branche `default` dans une construction `case...endcase`.

---

```

logic S0, S1, S2, S3, S4;

logic [1:0] E;

always@(*)

begin

S0 <= (E == 2'b00);

S1 <= (E == 2'b01);

S2 <= (E == 2'b10);

S3 <= (E == 2'b11);

end

```

---

L'opérateur `==` renvoie vrai ou faux en fonction du résultat de la comparaison. Donc ( $E == 2'b00$ ) renvoie vrai si les deux bits de  $E$  sont à 0 et faux sinon. Lorsque l'on affecte le booléen vrai à un signal (ici  $S0$ ), ce signal prend la valeur 1. De même, si on affecte le booléen faux à un signal, ce dernier prend la valeur 0<sup>10</sup>.

#### 1.4 Représentation des nombres

Jusqu'à présent, nous avons traité uniquement des variables logiques et réalisé des opérations logiques. Nous allons voir dans cette section comment des nombres peuvent être représentés et manipulés.

##### 1.4.1 Nombres entiers naturels

*Représentation générale* Un entier naturel  $N$  se représente, dans une base  $b$  par un  $n$ -uplet  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$  tel que<sup>11</sup> :

$$N = a_{n-1} \cdot b^{n-1} + a_{n-2} \cdot b^{n-2} + \dots + a_1 \cdot b^1 + a_0 \cdot b^0$$

10. Il aurait été possible d'utiliser la construction `if (E == 2'b00) S0 <= 1'b1; else S0 <= 1'b0;` mais elle est fortement déconseillée car très inélégante.

11. Attention, les opérateurs `+` et `*` reprennent ici leur signification mathématique classique, c'est-à-dire l'addition et la multiplication, contrairement au chapitre précédent où ils correspondaient aux opérateurs logiques OU et ET.

Dans cette représentation :

- $a_i$  est le chiffre de rang  $i$  et appartient à un ensemble de  $b$  symboles (0 à  $b - 1$ )

- $a_{n-1}$  est appelé le chiffre le plus significatif

- $a_0$  est appelé le chiffre le moins significatif

Les bases<sup>12</sup> les plus couramment utilisées sont :

- $b = 10$  : représentation décimale,  $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$

- $b = 16$  : représentation hexadécimale,

$a_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F\}$

- $b = 8$  : représentation octale,  $a_i \in \{0, 1, 2, 3, 4, 5, 6, 7\}$

- $b = 2$  : représentation binaire,  $a_i \in \{0, 1\}$ . Un chiffre binaire est également appelé *bit* (abréviation de l'anglais *binary digit*)

<sup>12</sup>. Dans la suite, en cas de risque de confusion, la base dans laquelle est représentée un nombre sera indiqué en indice, exemple :  $100_{(10)}$ ,  $100_{(2)}$ ,  $100_{(16)}$

*Représentation binaire non signée* Nous nous intéresserons dans la suite à la représentation des nombres en binaire (base 2). Dans cette base, un nombre entier naturel peut donc se représenter par le  $n$ -uplet  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0)$  tel que :

$$N = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \dots + a_1 \cdot 2^1 + a_0 \cdot 2^0$$

Où :

- $a_i$  est un bit (il appartient à un ensemble de 2 symboles : 0 ou 1)

- $a_{n-1}$  est appelé le bit le plus significatif (MSB : *Most Significant Bit*)

- $a_0$  est appelé le bit le moins significatif (LSB : *Least Significant Bit*)

*Conversion entre hexadécimal et binaire* Il est très simple de passer d'un nombre représenté en hexadécimal à un nombre représenté en binaire non signé. Il suffit de concaténer la représentation binaire sur 4 bits de chacun des chiffres hexadécimaux.

Exemple :

$$A1F_{(16)} = 1010\ 0001\ 1111_{(2)}$$

En effet :

$$\begin{aligned} A1F_{(16)} &= 10 \cdot 16^2 + 1 \cdot 16^1 + 15 \cdot 16^0 \\ &= (1 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 0 \cdot 2^0) \cdot 16^2 \\ &\quad + (0 \cdot 2^3 + 0 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0) \cdot 16^1 \\ &\quad + (1 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0) \cdot 16^0 \\ &= 1 \cdot 2^{11} + 0 \cdot 2^{10} + 1 \cdot 2^9 + 0 \cdot 2^8 \\ &\quad + 0 \cdot 2^7 + 0 \cdot 2^6 + 0 \cdot 2^5 + 1 \cdot 2^4 \\ &\quad + 1 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 \\ &= 1010\ 0001\ 1111_{(2)} \end{aligned}$$

De même, pour passer d'une représentation binaire non signée à une représentation hexadécimale, il suffit de regrouper les bits 4 par 4 (en partant des bits de poids faibles) et en transformant chacun des groupes en un chiffre hexadécimal.

Exemple :

$$10\ 1011\ 0000_{(2)} = 2B0_{(16)}$$

*Représentation binaire modulo* En pratique, sur le matériel, les nombres vont être représentés et manipulés sur un nombre fixe fini de bits. Donc un nombre  $N$  va être représenté, modulo  $2^n$ , sur  $n$  bits.

Sur  $n$  bits, il est donc possible de représenter les nombres entiers naturels compris dans l'intervalle  $[0, 2^n - 1]$ .

*En SystemVerilog* En SystemVerilog, il est souvent nécessaire de manipuler des constantes dans la description d'un module. Or, indiquer la valeur 10 dans un code est ambigu : dans quelle base doit être interprétée cette valeur (s'agit-il de  $10_{(2)}$  =  $2_{(10)}$ , de  $10_{(10)}$  ou de  $10_{(16)}$  =  $16_{(10)}$ ) et sur combien de bits doit être représentée cette valeur ?

Il est recommandé d'utiliser la construction SystemVerilog suivante afin d'être rigoureux :  $N'Bvvvv$  où :

- $N$  est le nombre de bits sur lesquels la valeur doit être représentée

- $B$  est la base dans laquelle la valeur qui suit est représentée :  $b$  pour binaire,  $h$  pour hexadécimal et  $d$  pour décimal

- $vvvv$  est la valeur de la constante dans la base  $B$

Exemples :

---

```

logic [3:0] P; // Vecteur de 4 bits

logic [7:0] Q; // Vecteur de 8 bits

logic [7:0] R; // Vecteur de 8 bits

always @(*)

begin

P <= 4'b1001;

// Identique à P <= 4'd9 ou P <= 4'h9

Q <= 8'h5A;

// Identique à Q <= 8'b01011010 ou P <= 8'd90

R <= 8'd127;

// Identique à R <= 8'b01111111 ou R <= 8'h7F

end

```

---

#### 1.4.2 Nombres entiers relatifs

Il existe plusieurs méthodes pour représenter les nombres entiers relatifs. La plus couramment utilisée est la représentation en *complément à 2* (CA2).

Comme vu précédemment, sur  $n$  bits, les nombres sont représentés modulo  $2^n$ , c'est-à-dire que  $2^n$  a la même représentation que 0,  $2^n + 1$  a la même représentation que 1, etc.

Si on étend ce principe aux nombres négatifs, il faudrait que  $-1$  ait la même représentation que  $2^n - 1$  (soit  $11\dots11_{(2)}$ ), que  $-2$  ait la même représentation que  $2^n - 2$  (soit  $11\dots10_{(2)}$ ), etc.

Par convention, dans la représentation en complément à 2, les nombres dont le bit de poids fort vaut 1 vont être considérés comme des nombres négatifs et les nombres dont le bit de poids fort vaut 0 vont être considérés comme des nombres positifs<sup>13</sup>.

En complément à 2, on peut donc représenter, sur  $n$  bits, les nombres signés compris dans l'intervalle  $[-2^{n-1}, 2^{n-1} - 1]$ .

13. Ce qui permet de garder une compatibilité avec la représentation non signée

Exemple de représentation sur 4 bits ( $n = 4$ ) :

| Binaire CA2 | Décimal | Binaire non signé | Décimal |

|-------------|---------|-------------------|---------|

| 1000        | -8      | 1000              | 8       |

| 1001        | -7      | 1001              | 9       |

| 1010        | -6      | 1010              | 10      |

| 1011        | -5      | 1011              | 11      |

| 1100        | -4      | 1100              | 12      |

| 1101        | -3      | 1101              | 13      |

| 1110        | -2      | 1110              | 14      |

| 1111        | -1      | 1111              | 15      |

| 0000        | 0       | 0000              | 0       |

| 0001        | 1       | 0001              | 1       |

| 0010        | 2       | 0010              | 2       |

| 0011        | 3       | 0011              | 3       |

| 0100        | 4       | 0100              | 4       |

| 0101        | 5       | 0101              | 5       |

| 0110        | 6       | 0110              | 6       |

| 0111        | 7       | 0111              | 7       |

D'un point de vue mathématique, un nombre  $N$  représenté en complément à 2 sur  $n$  bits par  $(a_{n-1}, a_{n-2}, \dots, a_0)$  vaut :

$$N = -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i$$

#### 1.4.3 Règles d'extension de signe

Les règles d'extension permettent de passer d'un nombre représenté sur  $n$  bits au même nombre représenté sur  $n + m$  bits.

*Entier non signé* Dans le cas non signé (entiers naturels), l'extension consiste à rajouter  $m$  bits à 0 en tête (poids fort).

Exemple :  $9_{(10)}$  se représente sur 4 bits non signés sous la forme  $1001_{(2)}$ . Sur 6 bits non signés, il se représente sous la forme  $001001_{(2)}$ .

*Complément à 2* Dans le cas d'un nombre représenté en complément à 2, l'extension est un peu plus complexe car il ne faut pas oublier que le bit de poids fort porte l'information du signe. Pour un nombre

en complément à deux, l'extension se fait en dupliquant le bit de poids fort.

Exemples :  $-7_{(10)}$  se représente sur 4 bits en complément à deux sous la forme  $1001_{(2)}$ . Sur 6 bits non signés, il se représente sous la forme  $111001_{(2)}$ .  $5_{(10)}$  se représente sur 4 bits en complément à deux sous la forme  $0101_{(2)}$ . Sur 6 bits non signés, il se représente sous la forme  $000101_{(2)}$ .

Preuve : Soit  $N = (a_{n-1}, a_{n-2}, \dots, a_0)$  un entier relatif représenté en complément à 2 sur  $n$  bits.

$$\begin{aligned} N &= -a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i \\ &= -a_{n-1}2^{n-1} \cdot (2-1) + \sum_{i=0}^{n-2} a_i 2^i \\ &= -a_{n-1}2^n + a_{n-1}2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i \\ N &= -a_{n-1}2^n + \sum_{i=0}^{n-1} a_i 2^i \end{aligned}$$

D'où  $N = (a_{n-1}, a_{n-1}, a_{n-2}, \dots, a_0)$  représenté sur  $n+1$  bits.

#### 1.4.4 Virgule fixe

Un nombre décimal  $D$  peut être approximé en base 2 par un vecteur  $(a_{n-1}, a_{n-2}, \dots, a_1, a_0, a_{-1} \dots a_{-m})$  tel que :

$$D = a_{n-1} \cdot 2^{n-1} + \dots + a_1 \cdot 2^1 + a_0 \cdot 2^0 + a_{-1} \cdot 2^{-1} + \dots + a_{-m} \cdot 2^{-m}$$

Où :

- $(a_{n-1}, \dots, a_0)$  est la partie entière de  $D$  (sur  $n$  bits)

- $(a_{-1}, \dots, a_{-m})$  est la partie fractionnaire de  $D$  (sur  $m$  bits)

- $2^{-m}$  représente la précision de cette approximation

Cette représentation est appelée représentation en virgule fixe<sup>14</sup>. Elle présente l'avantage de conserver les mêmes opérateurs d'addition et de soustraction que ceux des nombres entiers.

#### 1.4.5 Conclusion

En conclusion, lorsque l'on représente un nombre en binaire, il est très important de préciser la convention choisie (non signée, complément à 2, virgule fixe...) ainsi que le nombre de bits sur lequel est représenté ce nombre.

14. Fixe car une fois fixé le nombre de bits de la partie entière et de la partie fractionnaire, ils ne changent pas. Il existe d'autres méthodes, notamment la représentation en virgule flottante dont vous avez probablement déjà entendu parler qui est nettement plus complexe à mettre en œuvre au niveau des opérateurs arithmétiques et donc que nous n'aborderons pas dans ce cours.

### 1.5 Opérateurs arithmétiques

Dans cette section, nous allons présenter comment réaliser une addition et une soustraction, sur des nombres binaires (non signés ou en complément à 2), en utilisant les fonctions logiques de base introduites dans la section 1.2.

### 1.5.1 Addition

*Introduction* Il est possible d'additionner deux nombres binaires en utilisant l'algorithme élémentaire<sup>15</sup> consistant à additionner chaque chiffre des deux opérandes depuis les chiffres de poids faible vers les chiffres de poids fort et en propageant la retenue.

Exemple : Addition non signée de  $3_{(10)} = 11_{(2)}$  et  $2_{(10)} = 10_{(2)}$

$$\begin{array}{r}

& 1 \\

& 0 \ 1 \ 1 \\

+ & 0 \ 1 \ 0 \\

\hline

= & 1 \ 0 \ 1

\end{array}$$

15. Algorithme que vous avez appris à l'école primaire

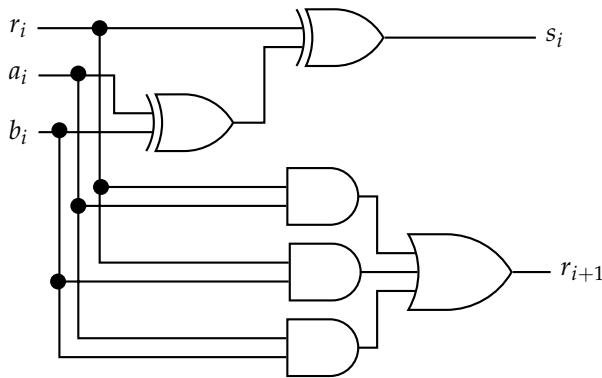

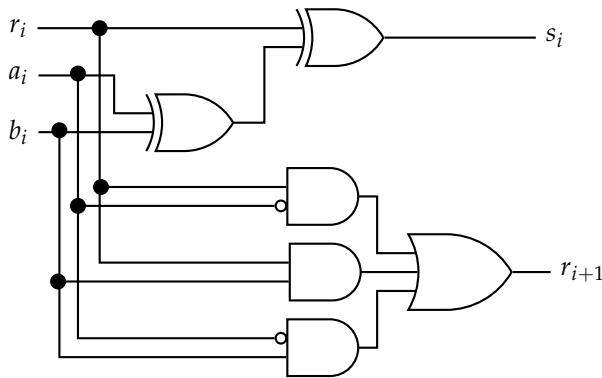

*Additionneur élémentaire* On a donc plusieurs additions élémentaires prenant en entrées un bit de chacun des deux opérandes du calcul ( $a_i$  et  $b_i$ ) et une retenue dite entrante ( $r_i$ ) venant de l'addition élémentaire précédente, et produisant en sortie un bit du résultat ( $s_i$ ) et une retenue dite sortante ( $r_{i+1}$ ) destinée à l'addition élémentaire suivante.

Cette addition élémentaire peut s'écrire arithmétiquement sous l'équation<sup>16</sup> :

$$a_i + b_i + r_i = 2 \cdot r_{i+1} + s_i$$

16. Le  $+$  et le  $\cdot$  représentent ici les opérateurs arithmétiques d'addition et de multiplication.

Les deux sorties  $r_{i+1}$  et  $s_i$  étant des booléens, il est possible d'exprimer leur valeur sous forme de fonctions booléennes des entrées  $a_i$ ,  $b_i$  et  $r_i$ . La table de vérité de cet opérateur d'addition élémentaire est la suivante :

| $a_i$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Décimal |

|-------|-------|-------|-----------|-------|---------|

| 0     | 0     | 0     | 0         | 0     | 0       |

| 0     | 0     | 1     | 0         | 1     | 1       |

| 0     | 1     | 0     | 0         | 1     | 1       |

| 0     | 1     | 1     | 1         | 0     | 2       |

| 1     | 0     | 0     | 0         | 1     | 1       |

| 1     | 0     | 1     | 1         | 0     | 2       |

| 1     | 1     | 0     | 1         | 0     | 2       |

| 1     | 1     | 1     | 1         | 1     | 3       |

D'un point de vue analytique on obtient les équations<sup>17</sup> suivantes :

17. Le  $+$  et le  $\cdot$  représentent ici les opérateurs logiques OU et ET.

$$\begin{aligned}

s_i &= a_i \oplus b_i \oplus r_i \\

r_{i+1} &= a_i \cdot b_i + a_i \cdot r_i + b_i \cdot r_i

\end{aligned}$$

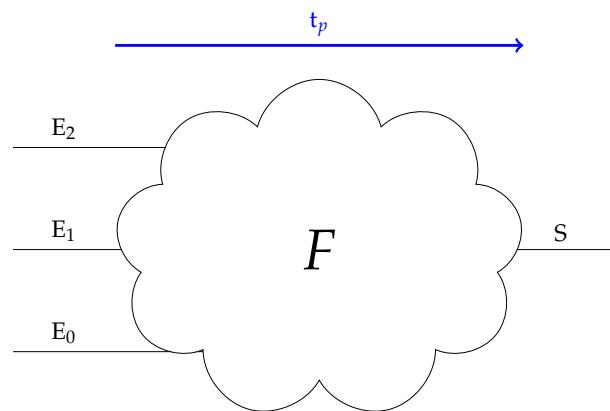

L'additionneur sur un bit peut être représenté par le schéma suivant :

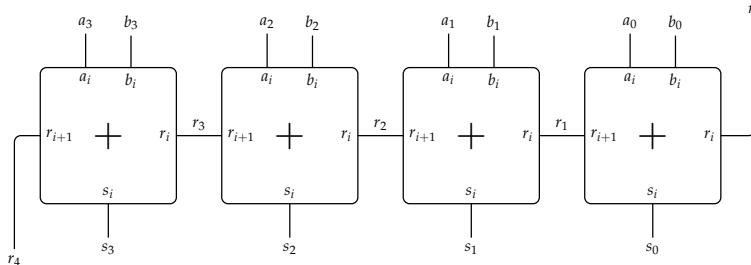

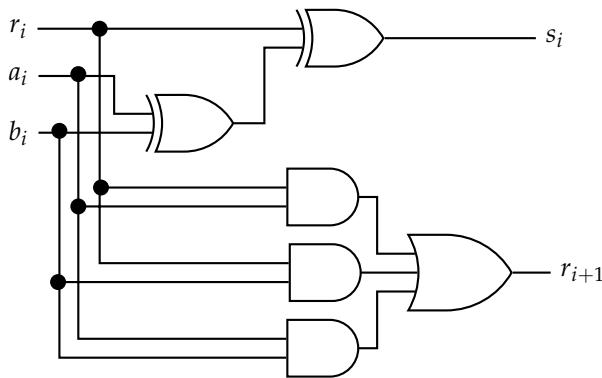

*Additionneur complet* Pour réaliser l'additionneur complet, il suffit de connecter ensemble des opérateurs élémentaires sur 1 bits<sup>18</sup> :

18. Cette structure est appelée additionneur à propagation de retenue. Il existe d'autres structures d'additionneur offrant des compromis entre le nombre d'opérateurs logiques utilisés et le temps de calcul différents.

*Dynamique de l'addition* Il faut faire attention au fait que l'addition de deux nombres binaires non signés (respectivement en complément à deux) sur  $n$  bits produit un résultat qui peut être représenté en non signé (respectivement en complément à deux) sur  $n + 1$  bits.

Afin d'être certain du résultat de l'addition d'un nombre non signé représenté sur  $n$  bits et d'un nombre non signé représenté sur  $m$  bits est d'étendre au préalable ces deux opérandes sur  $\max(n, m) + 1$  bits (en utilisant la règle d'extension vue précédemment dans la section 1.4.3). Le résultat, non signé, sera représenté sur  $\max(n, m) + 1$  bits. L'éventuelle retenue sortante de l'addition n'est pas à considérer.

De même, afin d'être certain du résultat de l'addition d'un nombre représenté sur  $n$  bits en complément à 2 et d'un nombre représenté sur  $m$  bits en complément à 2 est d'étendre au préalable ces deux opérandes sur  $\max(n, m) + 1$  bits (en utilisant la règle d'extension de signe vue précédemment dans la section 1.4.3). Le résultat sera représenté sur  $\max(n, m) + 1$  bits en complément à 2. L'éventuelle retenue sortante de l'addition n'est pas à considérer.

En SystemVerilog

---

```

logic [7:0] A;

logic [7:0] B;

logic [7:0] C;

logic retenue;

always @(*)

begin

{retenue, C} <= A + B;

// Si on n'a pas besoin de la retenue sortante, on peut

// écrire : C <= A + B;

end

```

---

L'addition de deux vecteurs de 8 bits produit en SystemVerilog un résultat sur 9 bits. Si ce résultat est affecté à un vecteur de 8 bits, seuls les 8 bits de poids faible sont gardés (addition modulo  $2^8$ ). L'opérateur {} qui permet de concaténer plusieurs signaux permet de récupérer, comme réalisé dans le code précédent, la retenue et le résultat du calcul.

### 1.5.2 Soustracteur

On peut également réaliser une soustraction de deux nombres à partir de soustracteurs élémentaires sur un bit.

*Soustracteur élémentaire* D'un point de vue arithmétique, on a<sup>19</sup> :

$$a_i - b_i - r_i = -2 \cdot r_{i+1} + s_i$$

La table de vérité correspondante est :

| $a_i$ | $b_i$ | $r_i$ | $r_{i+1}$ | $s_i$ | Décimal |

|-------|-------|-------|-----------|-------|---------|

| 0     | 0     | 0     | 0         | 0     | 0       |

| 0     | 0     | 1     | 1         | 1     | -1      |

| 0     | 1     | 0     | 1         | 1     | -1      |

| 0     | 1     | 1     | 1         | 0     | -2      |

| 1     | 0     | 0     | 0         | 1     | 1       |

| 1     | 0     | 1     | 0         | 0     | 0       |

| 1     | 1     | 0     | 0         | 0     | 0       |

| 1     | 1     | 1     | 1         | 1     | -1      |

D'un point de vue logique, si on exprime les sorties ( $r_{i+1}$  et  $s_i$ ) en fonction des entrées et des fonctions logiques élémentaires, on obtient<sup>20</sup> :

$$s_i = a_i \oplus b_i \oplus r_i$$

$$r_{i+1} = \overline{a_i} \cdot b_i + \overline{a_i} \cdot r_i + b_i \cdot r_i$$

19. Le + et le · représentent ici les opérateurs arithmétiques d'addition et de multiplication.

Ce soustracteur sur un bit peut être représenté par le schéma suivant :

20. Le + et le · représentent ici les opérateurs logiques OU et ET.

## 1.6 Du temps de propagation au temps de calcul

À cause des contraintes physiques liées à leur réalisation concrète<sup>21</sup>, les portes logiques ne peuvent pas changer d'état instantanément lorsque leurs entrées changent.

Le *temps de propagation* d'une porte, noté  $t_p$ , est le temps entre le changement de la valeur d'une entrée et la stabilisation de la valeur de la sortie de la porte.

Pendant ce laps de temps, la valeur de la sortie de la porte peut ne pas correspondre à la fonction logique réalisée avec les valeurs actuelles des entrées de la porte. Cette valeur de sortie ne doit donc pas être prise en compte durant cette période.

La prise en compte de ce temps de propagation va être importante pour déterminer la vitesse maximale de fonctionnement de l'implémentation d'une fonction logique et plus généralement le temps de calcul d'une fonction arithmétique quelconque.

### 1.6.1 Exemple de l'additionneur 1 bit

Soit l'additionneur complet sur 1 bit (tel qu'introduit en section 1.5.1) réalisé de la façon suivante :

Si on suppose que chacune des portes élémentaires (ici les XOR à deux entrées, les ET à deux entrées et le OU à trois entrées) ont toutes un temps de propagation  $t_p = 1$  ns, une fois les entrées  $a_i$ ,  $b_i$  et  $r_i$  stables, les sorties seront stables et correctes au bout de 2 ns. Le temps de propagation de cette implémentation de l'additionneur 1 bit est donc de 2 ns.

21. Un aperçu de la réalisation physique de ces portes en logique CMOS est donné dans le chapitre 5.

### 1.6.2 Exemple de l'additionneur à propagation de retenue

À partir de cet additionneur 1 bit, nous construisons un additionneur à propagation de retenue :

Une fois les entrées  $a_0, \dots, a_3, b_0, \dots, b_3$  et  $r_0$  stables, les sorties  $s_0$  et  $r_1$  du premier additionneur 1 bit seront stables au bout de 2 ns. Comme l'entrée  $r_1$  du deuxième additionneur 1 bit n'est stable qu'au bout de 2 ns, ses sorties  $s_1$  et  $r_2$  ne seront stables que 2 ns plus tard, c'est-à-dire au bout de 4 ns.

Donc, pour cet additionneur à propagation de retenue sur 4 bits, les sorties  $s_3$  et  $r_4$  ne seront stables qu'au bout de 8 ns. Le temps de propagation, ou temps de calcul, de cet additionneur est donc de 8 ns.

## 2

# *La logique séquentielle*

*Dans ce chapitre nous allons introduire la logique séquentielle synchrone en introduisant la notion de mémorisation (cf. section 2.1). Nous présentons ensuite la bascule D, élément mémorisant principal utilisé pour la mise en œuvre de la logique synchrone (cf. section 2.3) ainsi que les contraintes temporelles permettant de garantir le fonctionnement (cf. section 2.3.3). Enfin, nous présenterons quelques applications de la logique synchrone (cf. section 2.5).*

## *2.1 Mémorisation et logique séquentielle*

Les opérateurs logiques et les opérateurs de calcul combinatoires présentés au chapitre 1 ont la propriété suivante :

- Pour une même valeur des entrées présentées on obtient toujours la même valeur en sortie. En d'autre termes, les opérateurs combinatoires n'ont pas de mémoire.

De plus ces opérateurs possèdent un temps de propagation qu'il faut respecter pour être sûr que le résultat en sortie soit valide.

*Dans ce cas, comment utiliser ces opérateurs pour enchaîner plusieurs calculs consécutifs de façon fiable ?*

## *2.2 Logique séquentielle synchrone*

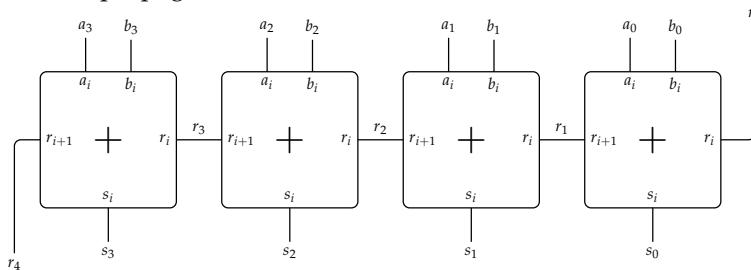

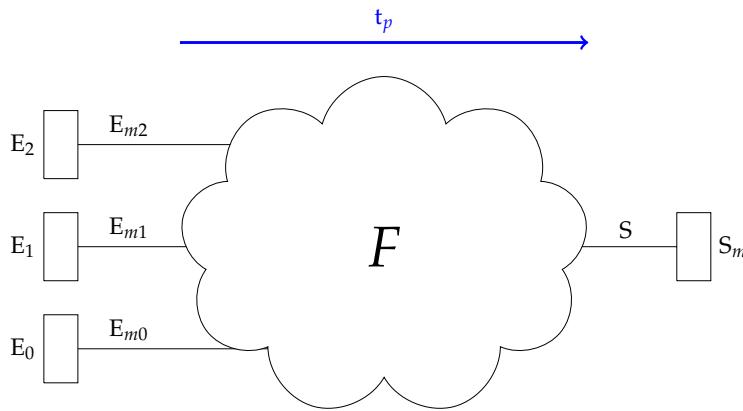

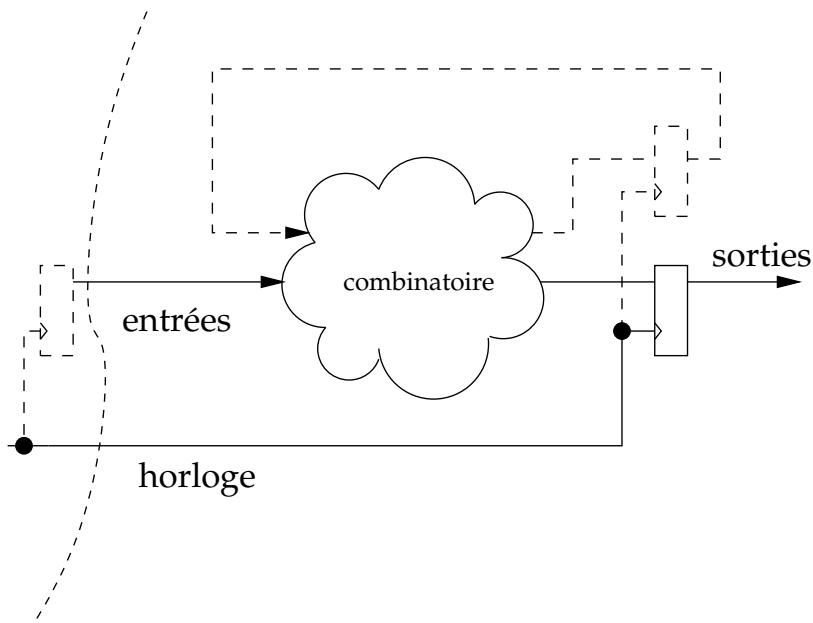

Prenons comme exemple la fonction combinatoire  $F$  de la figure 2.1.

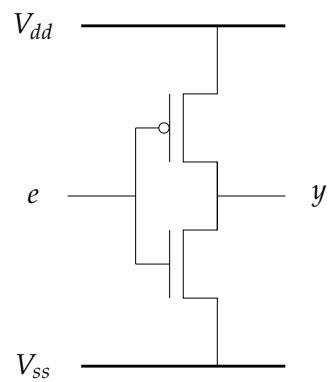

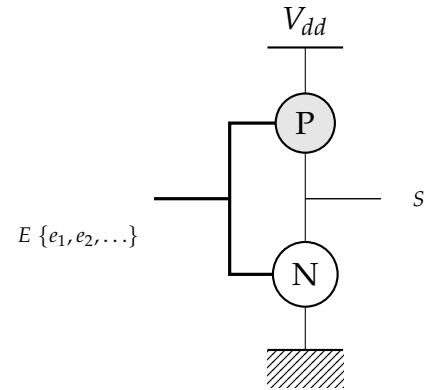

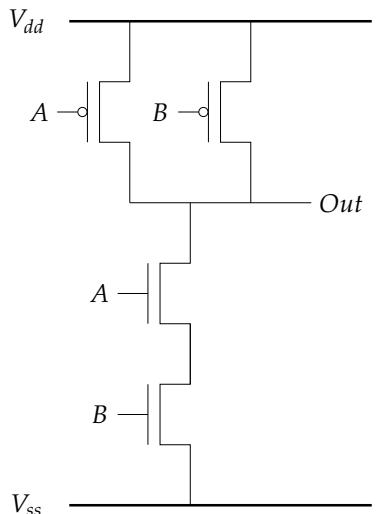

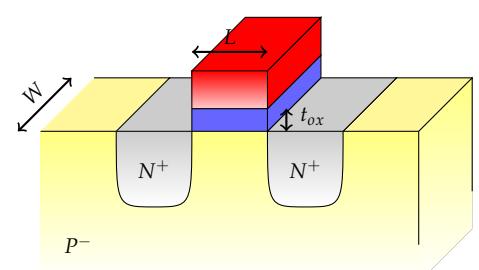

FIGURE 2.1: Un bloc combinatoire

Ce bloc a trois entrées  $E_0$ ,  $E_1$  et  $E_2$  et une sortie  $S$ . Si nous modifions l'une des entrées, il faut attendre  $t_p$  pour que le résultat soit valide.

Nous voulons enchaîner plusieurs calculs et obtenir la séquence suivante :

1.  $S(0) = F(E_0(0), E_1(0), E_2(0))$

2.  $S(1) = F(E_0(1), E_1(1), E_2(1))$

3.  $S(2) = F(E_0(2), E_1(2), E_2(2))$

4. ...

Il faut s'assurer que les entrées ne sont pas modifiées tant que la sortie n'est pas valide. Les entrées venant du monde extérieur ou d'un autre bloc de calcul, nous n'avons pas la garantie qu'elles restent stables.

Pour cela nous devons ajouter des éléments pour capturer les valeurs des entrées et les empêcher de changer durant le calcul, comme illustré sur la figure 2.2.

FIGURE 2.2: On capture les entrées pour les empêcher de changer durant un calcul

Pour se simplifier la tâche, la capture et la mémorisation des entrées se fera en même temps, de façon synchrone.

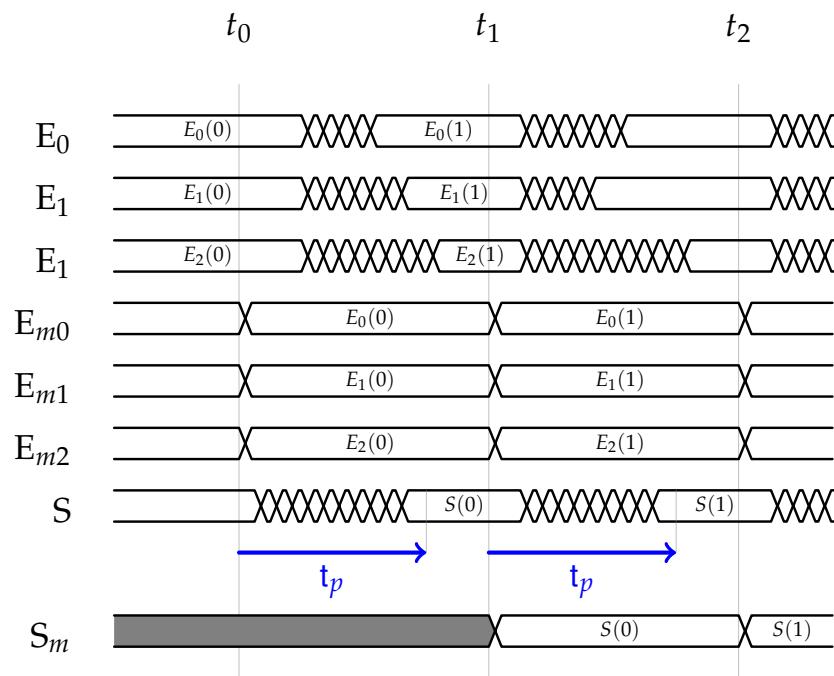

FIGURE 2.3: Chronogramme d'un calcul séquentiel synchrone

Une fois que nous sommes sûrs que le résultat est valide (après un temps  $t_p$ ), nous pouvons capturer le résultat en sortie et en même temps présenter de nouvelles valeurs sur les entrées.

La sortie, ainsi capturée, peut à son tour être utilisée comme entrée d'un autre bloc de calcul.

Tout ceci est résumé dans le chronogramme 2.3. Nous avons la séquence suivante :

- à l'instant  $t_0$  les entrées sont capturées (on dit aussi échantillonées)

- à  $t_0 + t_p$  la sortie du bloc combinatoire est valide

- à  $t_1 > t_0 + t_p$  la sortie est échantillonnée et de nouvelles entrées capturées

- et ainsi de suite ...

Cette logique est dite séquentielle synchrone. Nous avons la garantie que les calculs effectués sont corrects tant que l'intervalle entre les instants d'échantillonnage est supérieur au temps de propagation du bloc combinatoire.

Dans la suite, nous verrons quel composant est utilisé pour échantillonner et mémoriser les signaux et comment l'ensemble est synchronisé.

### 2.3 La bascule D

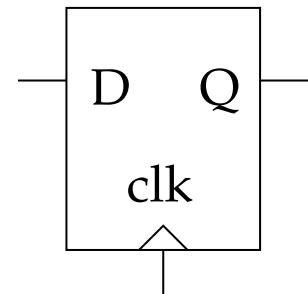

Le composant de base de la logique séquentielle synchrone est la *bascule D*. Elle peut aussi être appelée *dff* ou encore *flipflop* et parfois *registre*.

La figure 2.4 montre le schéma d'une bascule D. Une bascule D possède deux entrées et une sortie :

- Une entrée particulière, l'horloge **clk** symbolisée par un triangle.

- Une entrée pour la donnée, **D**.

- Une sortie pour la donnée mémorisée, **Q**.

L'horloge **clk** sert à synchroniser toutes les bascules d'un circuit. L'échantillonnage des signaux se faisant à chacun de ses fronts montants.

Le fonctionnement de la bascule D est le suivant :

- A chaque front montant de l'horloge **clk** (passage de 0 → 1) l'entrée **D** est copiée sur la sortie **Q**. On dit de la donnée est échantillonnée.

- Entre deux fronts d'horloge, la sortie **Q** ne change pas, elle est mémorisée.

Ce comportement peut, comme pour la logique combinatoire, être représenté par une table de vérité (voir la table 2.1).

#### Description SystemVerilog

Le bloc de code 2.1 est la description SystemVerilog d'une bascule avec une entrée **D** et une sortie **Q**. À chaque front montant (**posedge**) de l'horloge **clk**, l'entrée est copiée sur la sortie. Sinon, la sortie **Q** ne change pas d'état.

FIGURE 2.4: La bascule D

| D | clk | Q | → effet                  |

|---|-----|---|--------------------------|

| 0 | ↑   | 0 | → (copie de D sur Q)     |

| 1 | ↑   | 1 | → (copie de D sur Q)     |

| × | 0   | Q | → (Q conserve sa valeur) |

| × | 1   | Q | → (Q conserve sa valeur) |

| × | ↓   | Q | → (Q conserve sa valeur) |

TABLE 2.1: Table de vérité d'une bascule D

---

```

module dff (

input clk,

input D,

output logic Q

);

always @(posedge clk)

Q <= D;

endmodule

```

---

CODE 2.1: Description SystemVerilog d'une bascule D

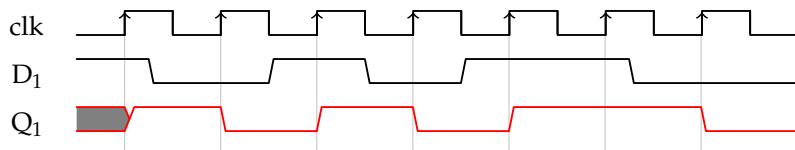

### 2.3.1 Utilisation des bascules D

#### 1. Échantillonnage :

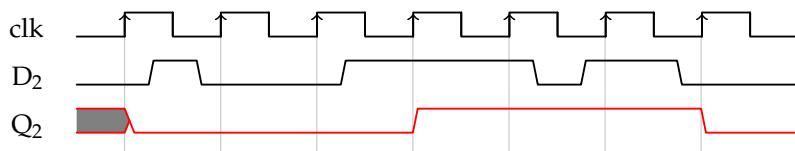

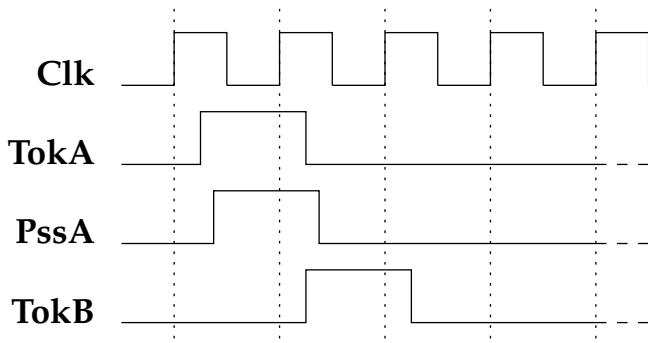

Une bascule D sert à échantillonner les données en entrée. Comme nous le voyons sur le chronogramme suivant, la valeur de l'entrée D est capturée à chaque front montant de l'horloge. Cette valeur est conservée jusqu'au front suivant.

#### 2. Filtrage :

Par son fonctionnement, une bascule D filtre les changements de son entrée qui se produisent entre les fronts de l'horloge. Comme le montre le chronogramme suivant, les changements sur le signal d'entrée de durée inférieure à la période de l'horloge n'apparaissent pas sur la sortie.

### 2.3.2 Les registres

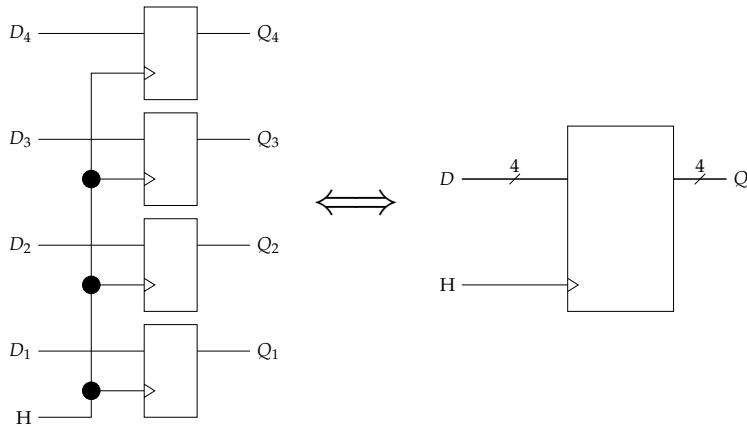

Comme nous sommes souvent amenés à manipuler des mots de plusieurs bits, on utilise pour cela plusieurs bascules. Cet assemblage de bascules D est appelé *registre*.

Le symbole d'un registre est le même que celui d'une bascule D. On peut préciser le nombre de bits manipulés sur l'entrée et la sortie du registre (voir la figure 2.5).

FIGURE 2.5: Un exemple de registre de 4bits de large

Description SystemVerilog

---

```

module dff (

input clk,

input[3:0] D,

output logic[3:0] Q

);

always @(posedge clk)

Q <= D;

endmodule

```

---

CODE 2.2: Description SystemVerilog d'un registre de 4bits

### 2.3.3 Les contraintes et les performances temporelles

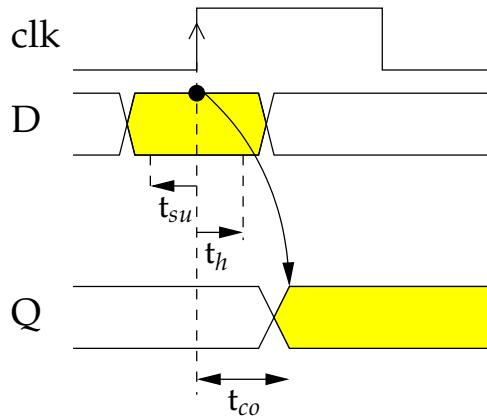

Pour qu'une bascule D fonctionne correctement, certaines précautions sont à prendre. En effet, les données présentées en entrée doivent être stables au moment du front de l'horloge. Ceci se traduit par des *contraintes temporelles* sur les signaux arrivant aux bascules.

La figure 2.6 schématisse ces contraintes. Pour une bascule D, les trois temps suivants, sont définis :

$t_{su}$  : temps de pré-positionnement (*setup*)

$t_h$  : temps de maintien (*hold*)

$t_{co}$  : temps de propagation (*clock to output*).

Pour que la bascule D fonctionne correctement, il faut que la donnée présentée en entrée soit stable au front d'horloge, il faut aussi que la donnée reste stable le temps que la mémorisation se fasse :

FIGURE 2.6: Contraintes temporelles d'une bascule D

- elle doit avoir atteint sa valeur  $t_{su}$  avant le front d'horloge,

- cette valeur doit être maintenue  $t_h$  après le front d'horloge.

La copie de l'entrée sur la sortie se fait avec un retard de  $t_{co}$ .

#### Performances d'un opérateur synchrone

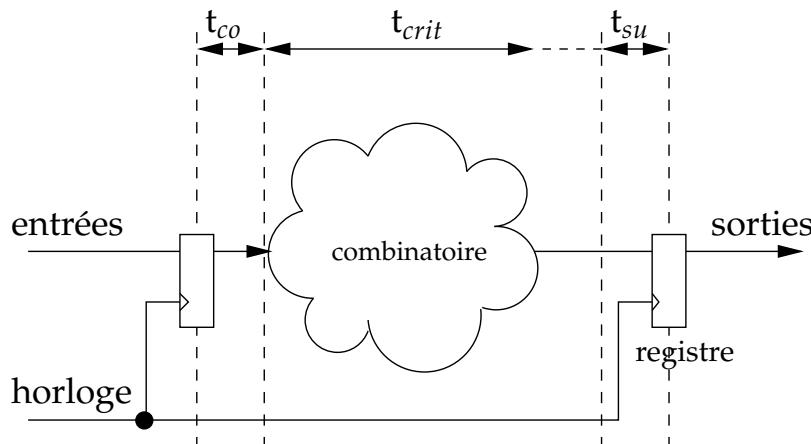

Comment calculer la fréquence maximale de fonctionnement d'un bloc de logique synchrone ?

FIGURE 2.7: Période minimale de l'horloge dans un bloc de logique séquentielle

Un bloc de logique synchrone, peut être vu comme un ensemble de blocs combinatoires précédés et suivis de registres. Les entrées de ces blocs combinatoires sortent des registres après un front d'horloge et les sorties sont échantillonnées au front suivant.

La période du signal d'horloge doit être suffisamment grande pour permettre aux sorties de tous les blocs combinatoires de se stabiliser avant le front où elles sont échantillonnées.

On définit ce qu'on appelle le chemin critique, comme le chemin qui a le temps de parcours le plus long dans les blocs combinatoires. On notera  $t_{crit}$  ce temps de parcours.

Résumons :

- Au front d'horloge les données en entrée sont échantillonnées.

- Au bout de  $t_{co}$  elles arrivent en entrée de blocs combinatoires.

- $t_{crit}$  plus tard on arrive aux bascules suivantes.

- Pour respecter les contraintes temporelles sur l'échantillonnage des bascules, il faut attendre au moins  $t_{su}$  avant d'échantillonner.

La figure 2.7 montre ce parcours.

Il faut donc que la période de l'horloge,  $T_{clk}$  vérifie :

$$T_{clk} > t_{co} + t_{crit} + t_{su}$$

Ou, exprimé en termes de fréquence de fonctionnement :

$$F_{clk} < F_{max} = \frac{1}{t_{co} + t_{crit} + t_{su}}$$

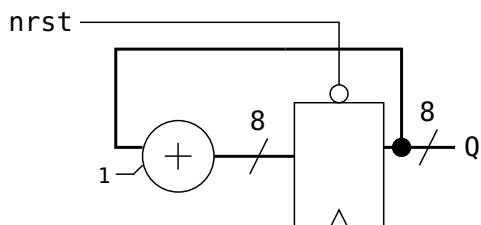

#### 2.3.4 L'initialisation

L'état initial d'une bascule D, au moment où le circuit est mis sous tension, n'est pas connu. Il dépend de plusieurs facteurs, parmi lesquels :

- la technologie utilisée pour la fabrication du circuit,

- l'architecture interne de la bascule,

- des micro-variations technologiques entre les éléments d'un même circuit,

- le bruit ambiant ...

Pour avoir un comportement prédictible, il faut pouvoir initialiser les bascules dans un état connu. Pour cela, un signal supplémentaire, que l'on peut contrôler, doit être utilisé. Ce signal particulier doit permettre de forcer l'état initial d'une bascule.

Si l'état initial est 0 on parle de *reset*. Si l'état initial est 1 on parle alors de *preset*.

*Remise à zéro asynchrone :*

Pour forcer l'état initial des bascules après la mise sous tension du circuit, on dispose généralement d'un signal supplémentaire de remise à zéro asynchrone. L'action de ce signal est globale, agissant sur toutes les bascules en même temps, indépendamment de l'horloge.

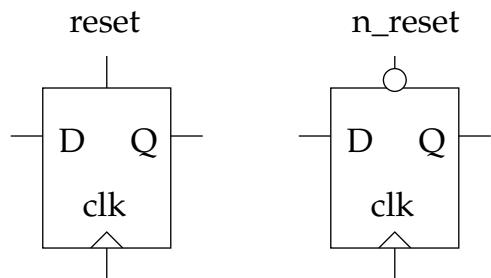

Les bascules possédant ce signal reset asynchrone sont représentées avec une entrée supplémentaire, comme on peut voir sur la figure 2.8.

FIGURE 2.8: Schéma de bascules D avec reset asynchrone.

Ce reset asynchrone peut être :

*positif* : initialise la bascule dès qu'il passe à 1

*négatif*: initialise la bascule dès qu'il passe à 0

Dans le schéma de la figure 2.8, le reset *négatif* est symbolisé par le rond, symbolisant l'inversion, sur l'entrée n\_reset.

L'effet d'un reset asynchrone est immédiat et la bascule est maintenue dans cet état initial tant que le signal reset est maintenu dans son état actif.

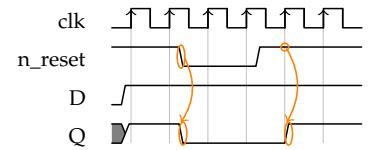

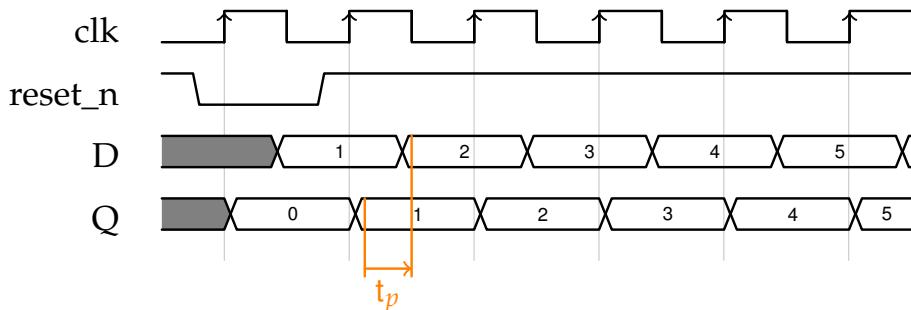

Le chronogramme 2.9 montre l'effet d'un reset asynchrone négatif. La sortie de la bascule est forcée à zéro dès que l'entrée n\_reset passe à 0. La bascule reste dans cet état jusqu'au front de l'horloge suivant le passage de l'entrée n\_reset à 1.

*Description SystemVerilog*

---

```

module dff (

input clk,

input n_reset,

input D,

output logic Q

);

always @ (posedge clk or negedge n_reset)

if (!n_reset)

Q <= 1'b0;

else

Q <= D;

endmodule

```

---

Remarquez que dans l'exemple de code 2.3 deux événements, (**posedge clk**) et (**negedge n\_reset**), déclenchent l'évaluation du processus **always**. Ceci veut dire que le passage à zéro de l'entrée n\_reset est pris en compte immédiatement.

*Remise à zéro synchrone* :

Une remise à zéro synchrone ou reset synchrone, est un forçage de l'état de la bascule qui prend effet au front d'horloge.

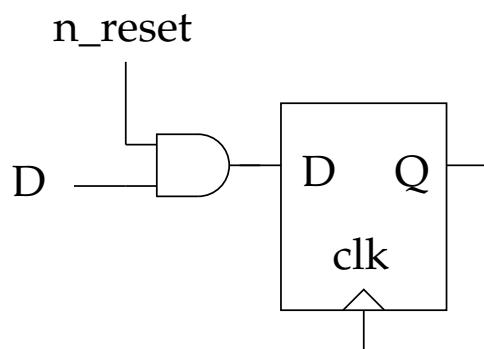

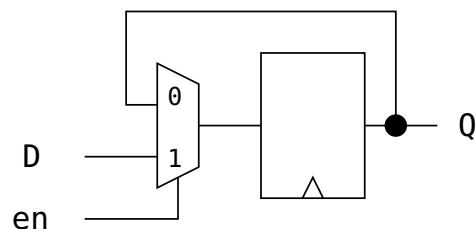

La figure 2.10 montre comment on peut construire une bascule avec un reset synchrone.

FIGURE 2.9: Chronogramme d'une remise à zéro asynchrone.

CODE 2.3: Bascule D avec remise à zéro asynchrone

FIGURE 2.10: Construction d'une bascule D avec reset synchrone.

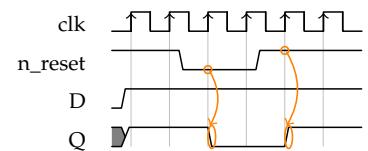

FIGURE 2.11: Chronogramme d'une remise à zéro synchrone.

Le chronogramme 2.11 montre comment cette remise à zéro synchrone se produit.

Le signal **n\_reset** est un de polarité négative, il agit sur la bascule quand sa valeur est 0. Au front de l'horloge, la bascule est forcée à zéro. Quand le signal **n\_reset** repasse à 1, la bascule retrouve son fonctionnement normal et la donnée en entrée est échantillonnée au front d'horloge.

Un reset synchrone doit respecter les mêmes règles que tout signal échantillonné par une bascule D.

En général, le reset synchrone est utilisé pour l'initialisation fonctionnelle d'une partie du circuit. Il est ainsi généré par une autre partie du circuit qui est elle aussi synchrone ce qui garanti qu'il a une durée d'au moins une période d'horloge.

*Description SystemVerilog*

---

```

module dff (

input clk,

input n_reset,

input D,

output logic Q

);

always @(posedge clk)

if(!n_reset)

Q <= 1'b0;

else

Q <= D;

endmodule

```

---

CODE 2.4: Bascule D avec remise à zéro synchrone

Remarquez que dans l'exemple de code 2.4 seul l'évènement (**posedge clk**) déclenche l'évaluation du processus **always**. Ceci veut dire que l'état de l'entrée **n\_reset** n'est testé qu'au front de l'horloge.

## 2.4 Généralisation

Un bloc générique de logique séquentielle est représenté en figure 2.12.

Dans un bloc de logique séquentielle on utilise la même horloge pour synchroniser l'ensemble des calculs. Tous les signaux venant du monde extérieur doivent être échantillonnés. Les sorties des blocs combinatoires doivent elles aussi être échantillonnées.

Ces sorties peuvent être :

- utilisées à l'extérieur (dans un autre bloc),

- redirigée vers les entrées de la logique combinatoire.

Dans le second cas nous parlons d'état interne. La valeur des sorties dépend alors de la valeur des entrées et de cet état interne.

FIGURE 2.12: Schéma générique d'un bloc de logique séquentielle synchrone

Pour que les valeurs consécutives des sorties soient prédictibles, il faut pouvoir forcer l'état initial. Ce qui est fait grâce à un signal externe d'initialisation.

## 2.5 Applications de la logique synchrone

Vous trouverez dans la suite quelques exemples d'applications de la logique synchrone.

### 2.5.1 Les registres à décalage

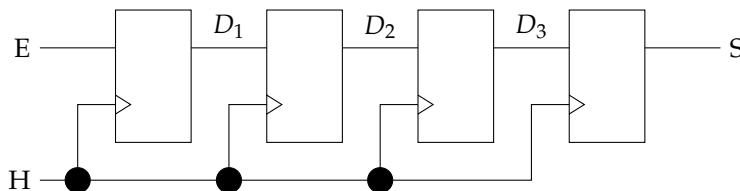

La figure 2.13 montre le schéma d'un registre à décalage composé de quatre bascules D mises en série. On peut aussi parler de registre à décalage d'une profondeur de 4.

Ce registre a comme entrée le signal E et comme sortie le signal S. Les signaux intermédiaires  $D_1$ ,  $D_2$  et  $D_3$  servent à relier la sortie d'une bascule à l'entrée de la bascule qui la suit.

Le chronogramme suivant montre le fonctionnement de ce registre à décalage.

Au premier coup d'horloge, l'entrée E est copiée en  $D_1$ . Puis aux coups d'horloge suivants, la valeur de E est décalée de proche en proche.

*Utilisation d'un registre à décalage :*

Un registre à décalage sert à retarder un signal d'un nombre entier de périodes d'horloge. Dans l'exemple précédent, la sortie S est une copie de l'entrée E avec quatre périodes d'horloge de retard.

Aussi, les sorties des bascules représentent l'histoire du signal E.

$$\begin{aligned} D_1 &= E(t-1) \\ D_2 &= E(t-2) \\ D_3 &= E(t-3) \\ S &= E(t-4) \end{aligned}$$

*Respect des contraintes temporelles :*

Nous avons vu, en section 2.3.3, que pour qu'une bascule fonctionne correctement il faut que le signal en entrée soit stable au moment du front d'horloge.

FIGURE 2.13: Schéma d'un registre à décalage composé de 4 bascules

Pour qu'un registre à décalage respecte cette contrainte, il faut que le temps de propagation de la bascule soit supérieur au temps de maintien.

C'est-à-dire :

$$t_{co} > t_h$$

Le respect de cette contrainte est garanti par construction par les concepteurs des bascules D.

*Description SystemVerilog*

---

```

module shift (

input clk,

input E,

output logic S

);

logic D1,D2,D3;

always @(posedge clk)

begin

D1 <= E;

D2 <= D1;

D3 <= D2;

S <= D3;

end

endmodule

```

---

CODE 2.5: Registre à décalage de profondeur 4

Remarquez dans l'exemple de code 2.5 que les signaux internes sont déclarés à l'intérieur du module.

De plus, dans un processus (**always**) les expressions utilisées à droite des affectations (**<=**) sont évaluées au moment de l'évènement déclenchant (ici le front montant de l'horloge). Ainsi les quatre affectations (**<=**) sont effectuées en même temps à chaque front montant de l'horloge. Leur ordre d'écriture dans le processus n'a donc pas d'importance.

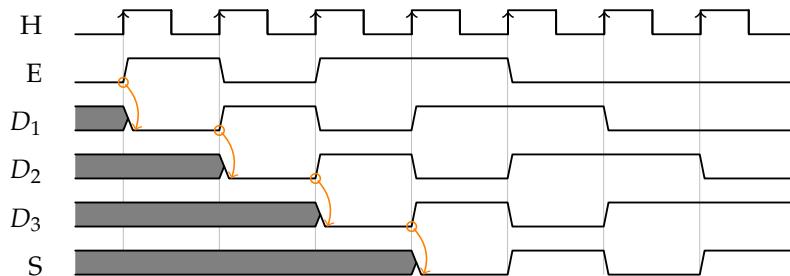

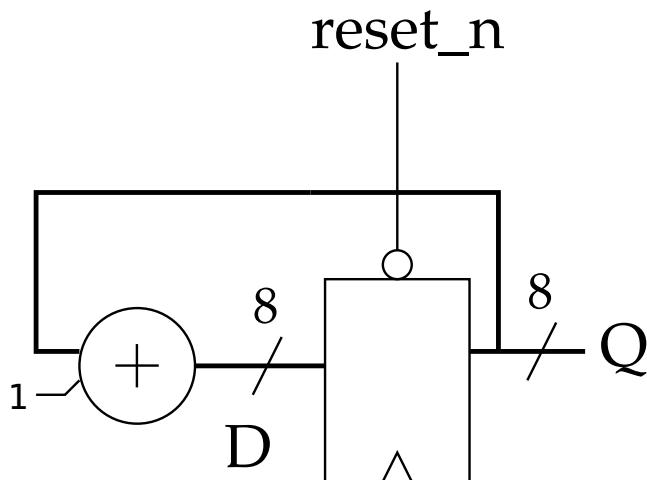

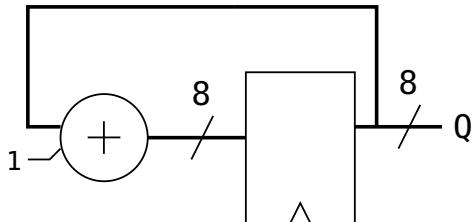

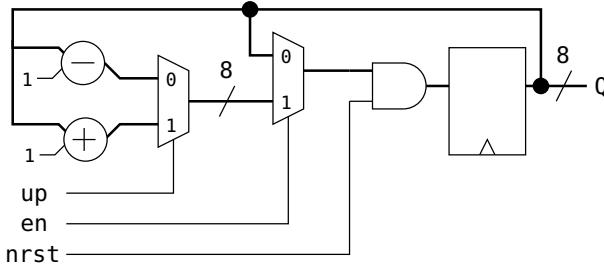

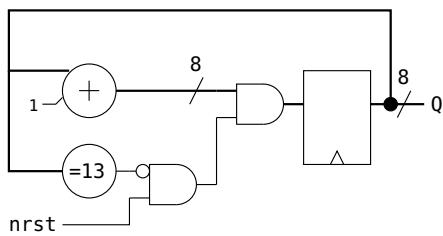

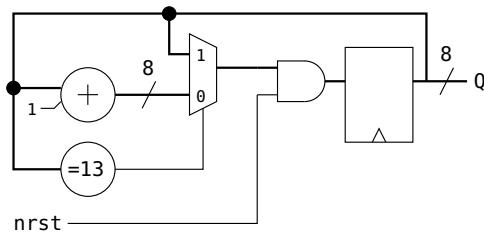

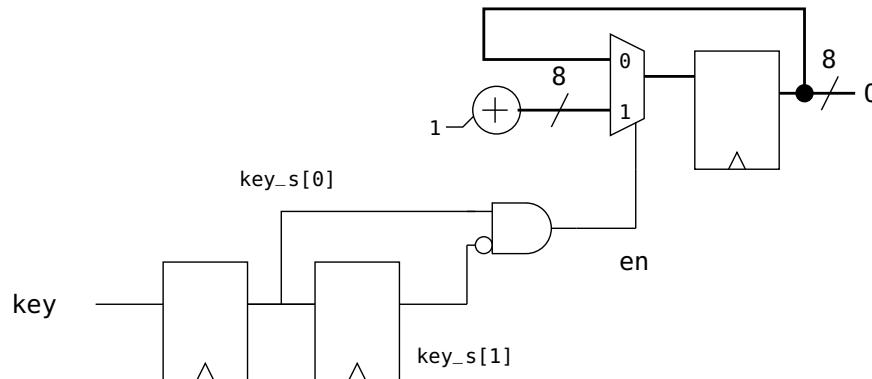

### 2.5.2 Les compteurs

Un compteur est un bloc de logique séquentielle synchrone de base. La sortie d'un compteur est incrémentée à chaque cycle d'horloge.

Pour construire un compteur il faut deux éléments :

- un registre, pour stocker la valeur (l'état) du compteur,

- un incrémenteur (additionneur avec 1) pour calculer les valeurs suivantes.

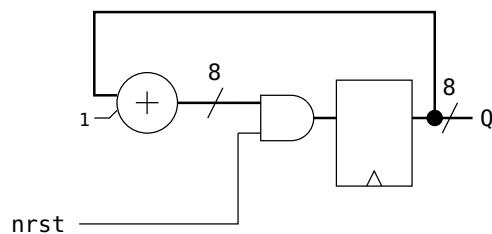

La figure 2.14 montre le schéma d'un tel compteur utilisant un registre et un addditionneur de 8 bits.

FIGURE 2.14: Schéma d'un compteur modulo 256

Le signal d'initialisation `reset_n` permet de forcer l'état initial et ainsi de commencer à compter à zéro. Ensuite, à chaque coup d'horloge, la valeur de `Q` est incrémentée.

Comme le nombre de bits du registre et de l'additeur est de 8, une fois arrivé à 255 le compteur repassera naturellement à 0. On parle de compteur modulo.

Le chronogramme suivant montre l'évolution des signaux dans le compteur. Ici l'action du signal de remise à zéro est synchrone.

Remarquez que le signal de remise à zéro agit sur la sortie du registre. Remarquez aussi que la sortie de l'additeur change après que la sortie du registre et que nous voyons apparaître son temps de propagation.

#### Description SystemVerilog

Remarquez que le signal interne `D` n'a pas besoin d'apparaître dans le code SystemVerilog. Quand nous écrivons `Q <= Q + 1` cela veut dire qu'au front d'horloge, la valeur du signal `Q` sera remplacée par son ancienne valeur plus `1`.

---

```

module cpt (

input clk,

input reset_n,

output logic[7:0] Q

);

always @(posedge clk)

if (!reset_n)

Q <= '0;

else

Q <= Q + 1;

endmodule

```

---

CODE 2.6: Compteur modulo 256 avec remise à zéro synchrone

### 2.5.3 Le “pipeline”

Le *pipeline* est une technique qui permet d’augmenter la fréquence de fonctionnement d’un bloc séquentiel. Elle est utile pour augmenter le débit de calcul sur un flux de données.

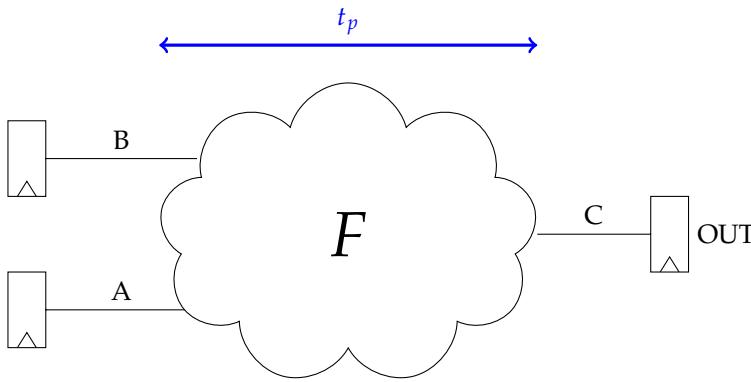

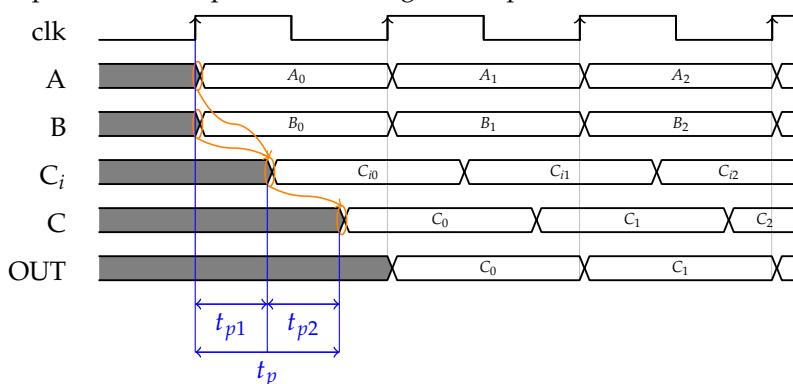

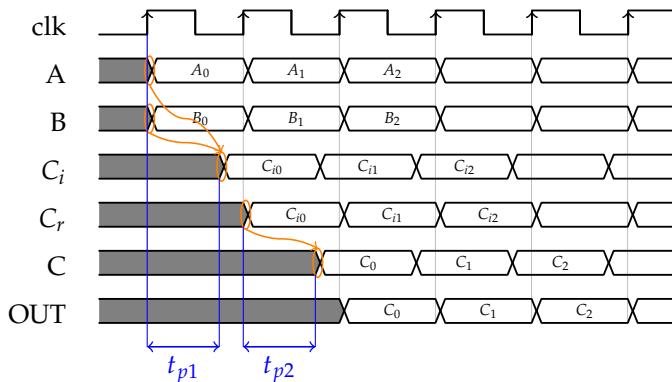

Considérons l’exemple suivant :

- Une fonction combinatoire  $F$  de temps de propagation  $t_p$

- Les données sont présentées sur les entrées A et B à la cadence de l’horloge clk de période  $T_{clk}$ .

*nb.* Pour simplifier les expressions, nous négligeons dans cet exemple les temps de propagations dans les registres.

Le système fonctionne correctement tant que la relation suivante, entre la période de l’horloge et le temps de propagation, est respectée :

$$t_p < T_{clk}$$

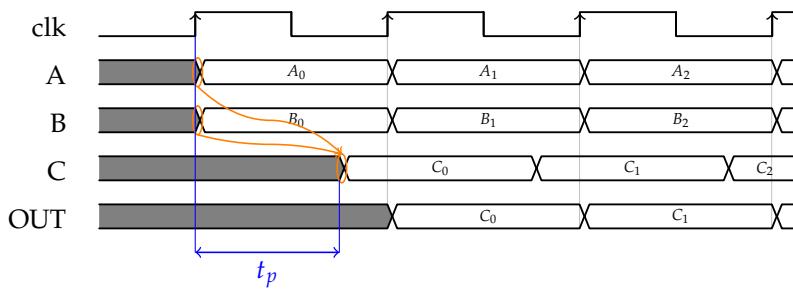

La sortie du bloc combinatoire C est échantillonnée et on obtient un résultat sur la sortie OUT à chaque période  $T_{clk}$ . Ce que montre le chronogramme suivant :

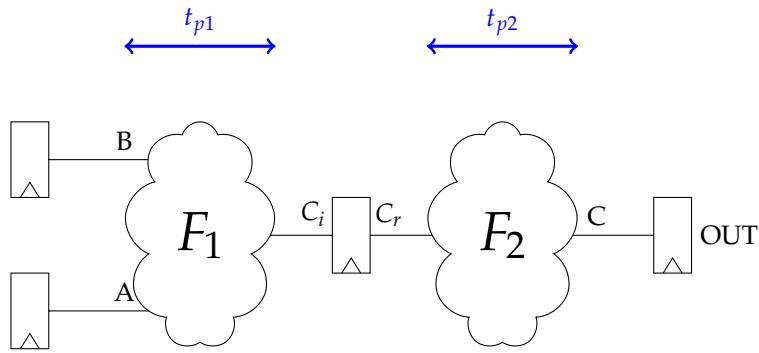

On décompose  $F$  en deux fonctions combinatoires  $F_1$  et  $F_2$  de temps de propagation respectifs  $t_{p1}$  et  $t_{p2}$ .

- On s'arrange pour avoir  $t_{p1} < t_p$  et  $t_{p2} < t_p$

$$t_{p1} \quad t_{p2}$$

Le point  $C_i$  représente l'ensemble des signaux reliant les deux blocs combinatoires  $F_1$  et  $F_2$ .

Le système fonctionne correctement tant que

$$t_{p1} + t_{p2} < T_{clk}$$

Dans le chronogramme suivant, nous avons pris  $t_{p1} + t_{p2} = t_p$  pour pouvoir le comparer au chronogramme précédent.

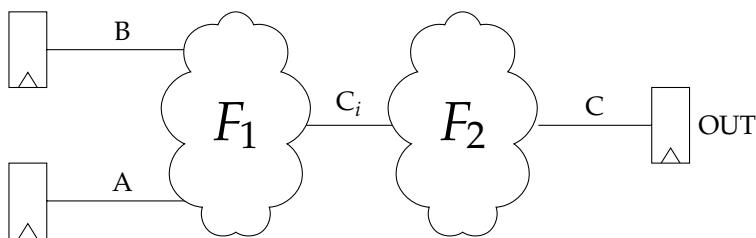

Ajoutons un registre entre les blocs combinatoires  $F_1$  et  $F_2$ . Les deux blocs sont maintenant précédés et suivis de registres.

Dans le jargon, nous disons que nous avons ajouté une couche de *pipeline*.

Le système fonctionne correctement si les deux conditions suivantes sont vérifiées :

$$\begin{cases} t_{p1} < T_{clk} \\ t_{p2} < T_{clk} \end{cases}$$

Mais comme les deux temps de propagation  $t_{p1}$  et  $t_{p2}$  sont inférieurs au temps de propagation initial  $t_p$ , nous pouvons réduire la période de l'horloge  $T_{clk}$ .

Ou augmenter ainsi la fréquence de fonctionnement et donc la cadence à laquelle les calculs sont faits. Ce qui est illustré dans le chronogramme suivant :

Remarquez que le premier résultat arrive sur la sortie OUT au bout de deux périodes de l'horloge.

Résumons :

- Le *pipeline* permet d'augmenter la fréquence de fonctionnement.

- La latence initiale augmente du nombre de couches de *pipeline*.

- On a augmenté la complexité et la taille du circuit en ajoutant des bascules et en modifiant le bloc combinatoire initial.

# 3

## Les unités de contrôle

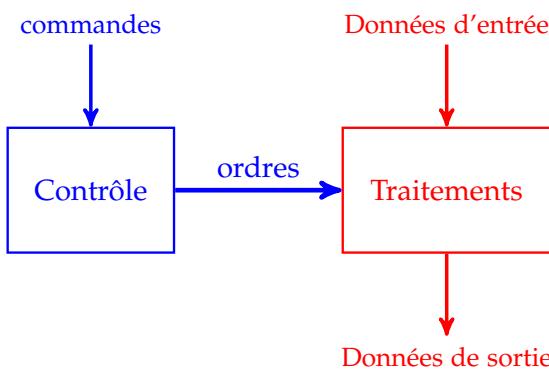

Les architectures classiques de traitement numérique sont traditionnellement découpées en **Unités de Traitement** et **Unités de Contrôle**.

Les **Unités de Traitement** sont en charge du traitement proprement dit des données. L'**Unité Arithmétique et Logique** d'un microprocesseur est un exemple d'unité de traitement : Elle reçoit des données interprétées comme des entiers, et réalise des opérations arithmétiques simples (addition, soustraction,..) ainsi que des opérations booléennes sur ces données. Pour opérer convenablement, c'est-à-dire exécuter **la bonne opération au bon moment**, ces unités de traitement reçoivent des **ordres** par l'intermédiaire de **signaux de contrôle**.

Le **Unités de Contrôle** sont en charge de générer ces signaux de contrôle, en s'appuyant sur la connaissance du passé (l'**état** courant du système) et sur des sollicitations extérieures (les **commandes**). En clair, ce sont des **automates** matériels.

Ce chapitre décrit donc les structures nécessaires à la réalisation d'automates matériels ainsi que les techniques de codage SystemVerilog associées.

FIGURE 3.1: Système numérique partagé en unité de contrôle et unité de traitement

### 3.1 Automates matériels synchrones

#### 3.1.1 Gestion de l'évolution des états

Les automates matériels synchrones peuvent être construits de la façon suivante :

- L'état courant de l'automate est codé dans un registre (ensemble de bascules D) synchrone.

- La taille du registre (nombre de bits) définit ainsi le nombre d'états maximum pouvant être codés.

- L'initialisation du registre permet d'imposer un état de départ à l'automate.

- En fonction de l'**état courant** et des entrées (les **commandes**) un **état futur** est calculé combinatoirement.

— Au front d'horloge, le registre est mis à jour : l'état futur devient l'état courant.

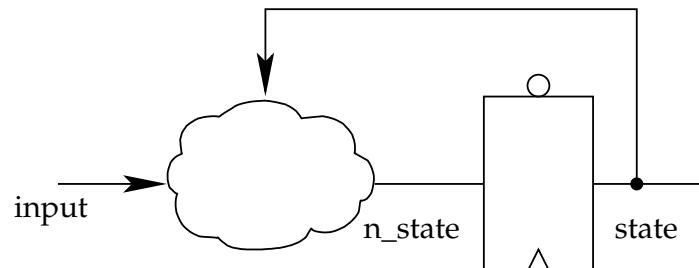

Le schéma de la figure 3.2 décrit la structure matérielle correspondante. Le nuage représente le bloc de calcul combinatoire. Remarquons que les signaux d'entrée des bascules codent **l'état futur (n\_state)**, alors que les signaux de sortie des bascules codent **l'état courant (state)**.

FIGURE 3.2: Structure matérielle pour l'évolution des états

### 3.1.2 Génération des signaux de contrôle

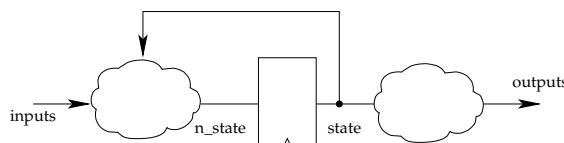

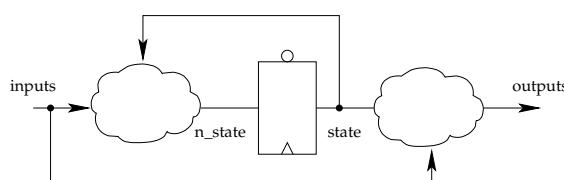

Un automate, n'a de sens que s'il sert à piloter une unité de traitement. Pour cela, un bloc de calcul combinatoire est en charge de créer les signaux de contrôle, soit simplement à partir de l'état courant (dans la littérature on appelle cela machine de Moore), soit à partir de l'état courant et des entrées du contrôleur (dans la littérature on appelle cela machine de Mealy). Les figures 3.3 et 3.4 représentent respectivement les schémas d'une machine de Moore et d'une machine de Mealy. Suivant la situation, l'une ou l'autre est plus adaptée.

FIGURE 3.3: Structure matérielle pour le calcul des sorties (Moore)

FIGURE 3.4: Structure matérielle pour le calcul des sorties (Mealy)

### 3.2 Codage SystemVerilog des automates

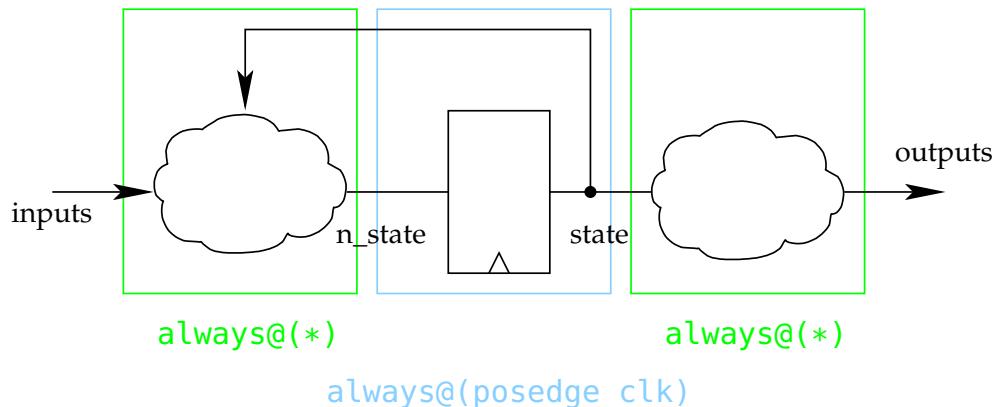

En s'appuyant sur les schémas précédents la traduction en code SystemVerilog est assez directe comme l'indique la figure 3.5 :

FIGURE 3.5: Processus SystemVerilog pour un automate synchrone

- Un processus combinatoire se charge de calculer les états futurs

- Un processus synchrone se charge de la mise à jour des états

- Un ou plusieurs processus combinatoires génère(nt) les signaux de contrôle.

#### 3.2.1 Utilisation de types énumérés pour décrire des états

Il est possible, en SystemVerilog, de définir des vecteurs de booléens sous la forme de type énumérés par l'utilisation du mot-clé `enum`.

- Par défaut, les valeurs énumérées correspondent aux codes **0, 1, 2, 3 ...** en partant de la première valeur.

- La taille nécessaire au codage des différentes valeurs est définie dans la définition du vecteur `logic`.

Le code 3.1 décrit la définition de signaux `state` et `n_state` sous la forme de types énumérés. Ces signaux représentent respectivement l'état courant et l'état futur de notre automate. Il est possible ensuite d'utiliser directement les noms symboliques pour calculer des affectations ou faire des comparaisons.

---

```

...

// state et n_state doivent être déclarés conjointement

enum logic[2:0] {SWAIT, S1, S2, S3, S4, S5, S6} state, n_state ;

...

always@(*) begin

n_state <= S1;

if(state == SWAIT) begin

...

end else begin

...

end

```

---

CODE 3.1: Les états sous forme de type énuméré

### 3.2.2 Codage de la mise à jour de l'état

Le code 3.2 est un exemple de définition du registre d'état. Attention : Il ne faut pas oublier l'initialisation qui permet de définir l'état de départ de l'automate. Dans l'exemple suivant, on choisit de placer l'automate dans l'état **SWAIT** si le signal **reset** vaut **1** au front montant de l'horloge (initialisation synchrone). On aurait pu aussi choisir une initialisation asynchrone.

---

```

always@( posedge clk)

if(reset)

state <= SWAIT;

else

state <= n_state;

end

```

---

CODE 3.2: Le registre d'états

### 3.2.3 Codage de l'évolution d'un automate

La construction **case** permet de traduire facilement la table d'évolution des états. Nous pouvons ainsi regrouper dans un même vecteur (les accolades servent à concaténer des éléments dans un vecteur) l'ensemble des signaux d'entrée et l'état courant de manière à définir la **table d'évolution des états** de manière très régulière. Remarquez, dans le code 3.3, l'usage du mot-clef **default** pour définir le cas par défaut, c'est-à-dire le fait de ne pas changer d'état.

---

```

always@(*)

case ( {state, entree_1, entree_2} )

{SWAIT,1'b0, 1'b1} : n_state <= S1;

{S1  ,1'b1, 1'b1} : n_state <= S2;

...

default           : n_state <= state;

endcase

```

---

CODE 3.3: Le calcul de l'état futur

### 3.2.4 Extension de la construction **case** : le mot-clef **casez**

Il peut parfois être long et fastidieux de donner explicitement tous les cas. Lorsque certains signaux ne sont pas utiles dans les équations de transition, il est possible de les représenter par le caractère «**?**». Dans ce cas le mot-clé **case** doit être remplacé par **casez** comme indiqué dans le code 3.4

Dans l'exemple précédent, on passe de l'état **S1** à l'état **S2** indépendamment de la valeur du signal **entree\_2**.

---

```

always@(*)

casez ( {state, entree_1, entree_2} )

{WAIT, 1'b0, 1'b1} : n_state <= S1;

{S1, 1'b1, 1'b?} : n_state <= S2;

...

default : n_state <= state;

endcase

```

---

CODE 3.4: Exemple d'utilisation du mot-clé **casez**

### 3.2.5 Utilisation des constructions **if** et les transitions par défaut

Dans certains cas, il est plus simple et plus lisible d'exprimer les conditions de transitions en utilisant la construction **if**.

Une astuce de codage permet de réduire la complexité du code en prévoyant un cas par défaut dans lequel on reste dans l'état courant. Comme le montre l'extrait de code 3.6, les **if** ne servant à exprimer que les changements d'état.

Notez l'utilisation obligatoire de **begin...end** pour délimiter les blocs de code.

---

```

always@(*)

begin

// cas par défaut, on reste dans l'état courant

// n_state vaudra cette valeur si aucune autre condition n'est vérifiée

n_state <= state;

casez (state)

WAIT : begin

if (entree_1) n_state <= S1;

if (entree_2) n_state <= S2;

// si aucune condition n'est vérifiée, on sait que n_state

// vaudra state et qu'on reste dans l'état courant

end

S1 : begin

if (entree_3) n_state <= S3;

...

end

...

// ici le cas default n'est pas obligatoire

endcase

end

```

---

CODE 3.5: Utilisation de **case** et **if** pour les transitions d'états

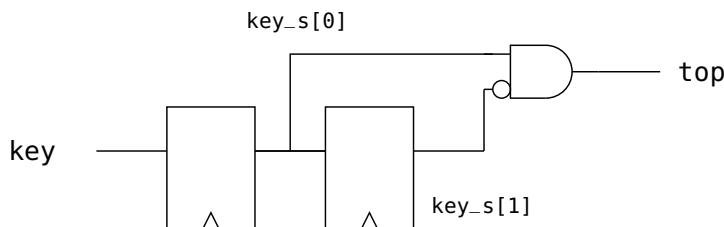

### 3.2.6 Codage des signaux de sortie (signaux de contrôle).

Pour des raisons de facilité de lecture, il est recommandé d'écrire un processus combinatoire par signal de sortie. Cela permet souvent d'éviter des codes trop complexes à base de **case** et de **if** imbriqués, difficiles à lire et à corriger. La règle étant de ne pas mélanger dans un même processus **always** des codes qui n'ont rien de commun.

Le code 3.6 est un exemple de génération de signaux de contrôle. Dans cet exemple, on imagine qu'une unité de traitement est capable de calculer des divisions et démarre un traitement si le signal **start\_div** est égal à **1**.

Le contrôleur reçoit la commande **ask\_div** mais ne donne l'ordre au diviseur de démarrer que lorsque il est dans l'état **START\_COMPUTATION**.

Enfin, le contrôleur génère un signal **end\_of\_computation** dès qu'il atteint l'état **END\_OF\_COMPUTATION**.

Notez qu'en SystemVerilog, il y équivalence entre une expression booléenne et un bit.

---

```

always@(*) start_div <= (state==START_COMPUTATION) && ask_div;

always@(*) end_of_computation <= (state==END_OF_COMPUTATION);

```

---

CODE 3.6: Exemple de codage de signaux de contrôle

# 4

## *Le nano processeur*

*Dans ce chapitre nous allons présenter comment concevoir un microprocesseur à partir d'un exemple simple et progressif. Nous introduisons la notion de programme (cf. section 4.1) ainsi que la mémoire servant à le stocker (cf. section 4.2). Dans la suite du chapitre nous faisons évoluer l'architecture du processeur pour permettre d'exécuter des programmes de plus en plus complexes.*

### *4.1 Programme, instructions et données*

Les processeurs ne sont rien d'autre que des machines à calculer *programmables*. Imaginez que vous êtes comptable, et que vous avez à effectuer une série d'opérations qu'on vous a gentiment inscrites sur une feuille de papier.

Voici un exemple d'instructions qu'on peut vous avoir donné :

---

```

1 faire 112 + 3

2 faire 4 + 5

3 faire 2 + 16

4 faire ...

```

---

Vous pouvez avoir des enchaînements un peu plus complexes, par exemple :

---

```

1 faire 112 + 4

2 faire "résultat précédent" + 1

3 ...

```

---

pour lesquels vous devez mémoriser des résultats intermédiaires. Et si on vous demande vraiment de réfléchir, de raisonner et de prendre des décisions, vous vous retrouverez avec :

---

```

1 faire 112 + 3

2 faire "résultat précédent" - 4

3 faire si "le résultat est nul" alors "passer à l'étape" 6,

4     sinon "continuer"

5 faire 3 * 4

6 faire "résultat précédent" + 9

7 faire "ouvrir la fenêtre"

8 faire "résultat de l'étape" 2 - 15

9 faire "passer à l'étape" 12

10 faire ...

```

---

Un microprocesseur est un dispositif électronique qui peut faire ce travail à votre place. Il ne reste qu'à rendre cette feuille de papier lisible par ce dispositif électronique.

Examinons un peu plus le texte de la feuille de papier pour essayer de trouver les éléments important qu'il faut faire « comprendre » au processeur.

Ce texte est une série<sup>1</sup> d'opérations ou d'actions à effectuer, c'est ce qu'on appelle un « **programme** ».

Dans ce programme on distingue deux types d'éléments :

— **les données :**

- d'abord les **opérandes** proprement dits (3, 4, 112, ...),

- et les opérandes implicites (« **résultat précédent** », « **résultat de l'étape 2** », ...);

— **les instructions :**

- pour nous ce sont principalement les opérations arithmétiques (« + », « - », « \* », « / » ...),

- il y a aussi des tests (« **si le résultat précédent est nul ...** »),

- et des sauts (« **passer à l'étape 12** »), souvent conditionnés par un test (« **alors passer à l'étape 6** »),

- ainsi que des instructions spéciales (« **ouvrir la fenêtre** »).

<sup>1</sup>. Notez que ces opérations sont numérotées : elles ont un **ordre**.

Dans le premier exemple, l'ordre n'a pas tellement d'importance, mais il en a une dans les deux suivants quand on parle de « **résultat précédent** », l'**« étape 6 »**, ...

Résumons :

- Un programme est une suite ordonnée d'instructions.

- Une instruction permet :

- d'agir sur des opérandes en utilisant des opérateurs,

- d'agir sur le flot d'exécution du programme.

## 4.2 La mémoire RAM

Comme le processeur est un dispositif électronique numérique, il ne peut interpréter que des niveaux logiques (1 ou 0). Il faudra donc « **encoder** » les instructions et les données de notre programme en une série de **bits** (des 1 et 0 donc des nombres).

La feuille de papier doit être elle aussi remplacée par dispositif électronique permettant de stocker ces nombres et de les modifier pendant l'exécution du programme. Cette mémoire électronique doit aussi permettre d'accéder aux éléments qu'elle contient dans n'importe quel ordre (de façon aléatoire).

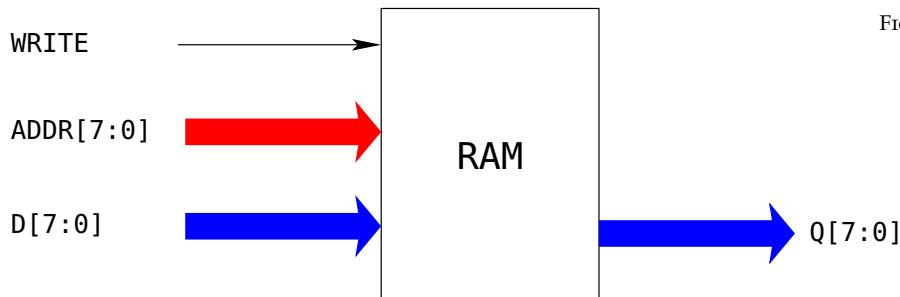

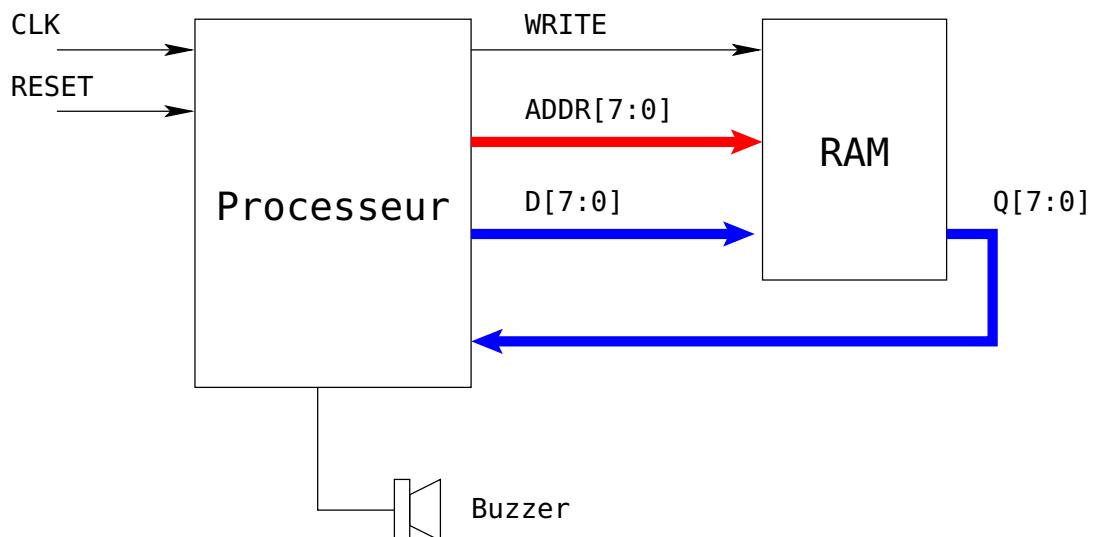

Ce type de mémoire est appelé « **RAM** » (Random Access Memory). La figure 4.1 montre le schéma de l'interface d'une RAM simple pouvant contenir 256 mots de 8 bits.

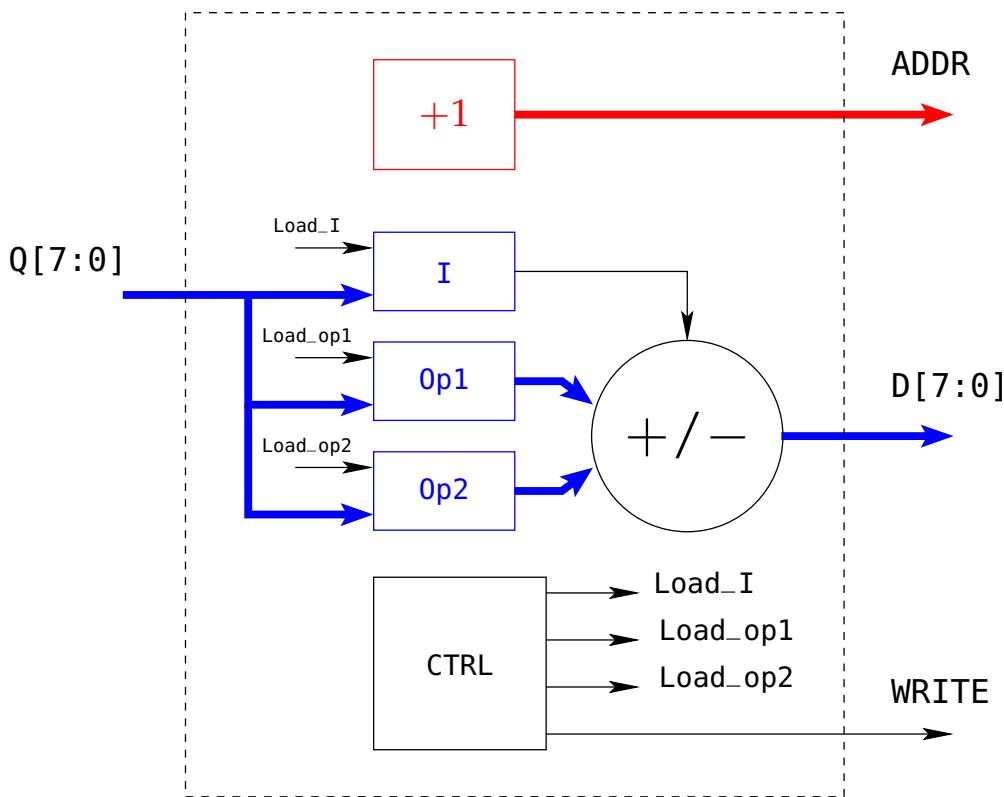

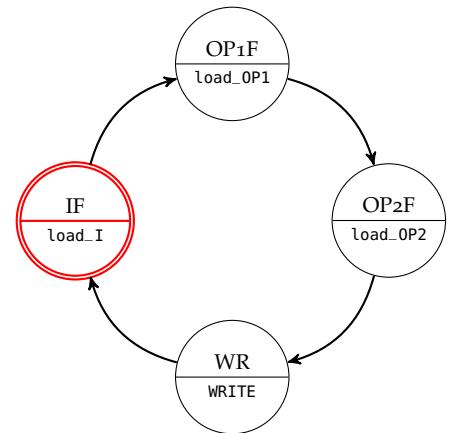

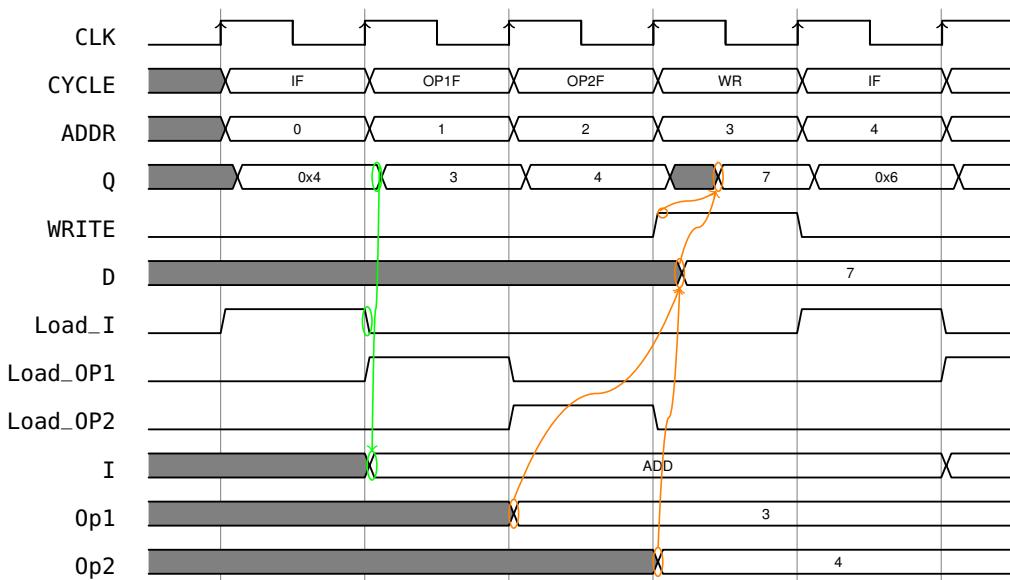

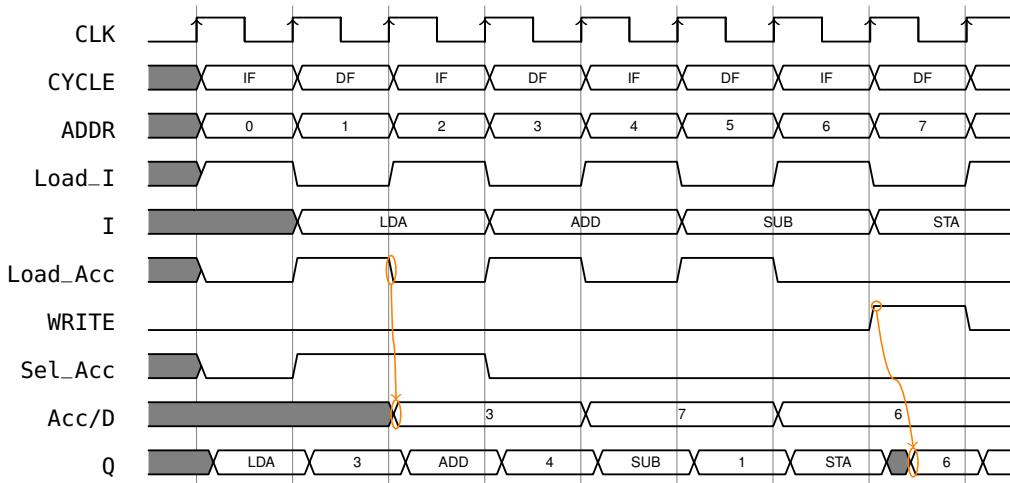

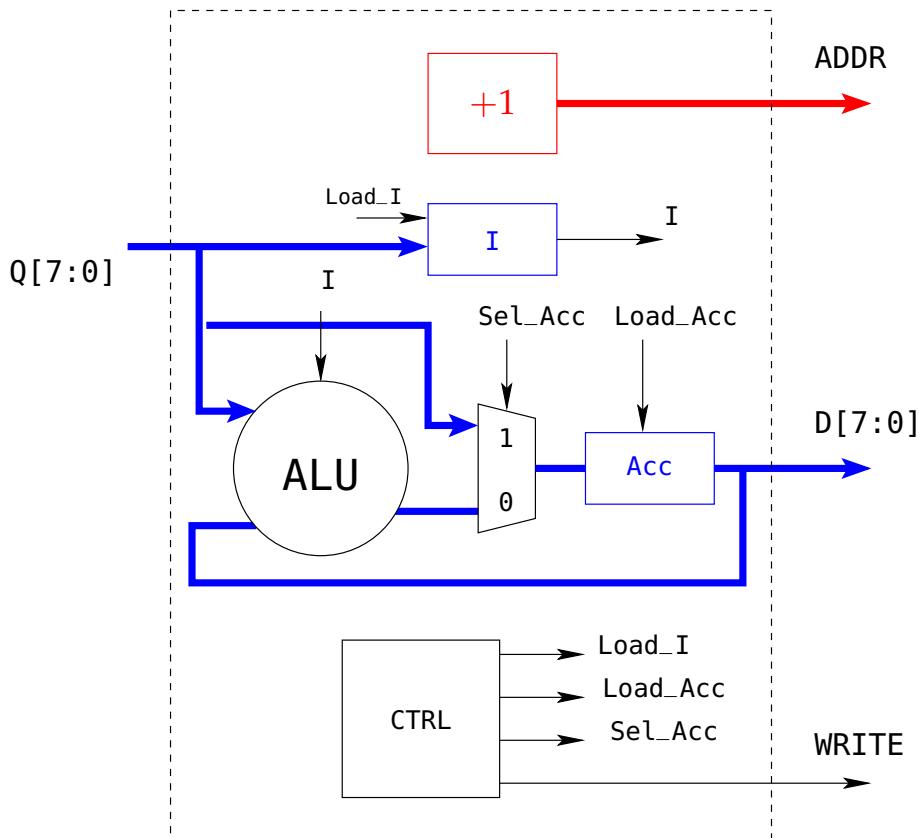

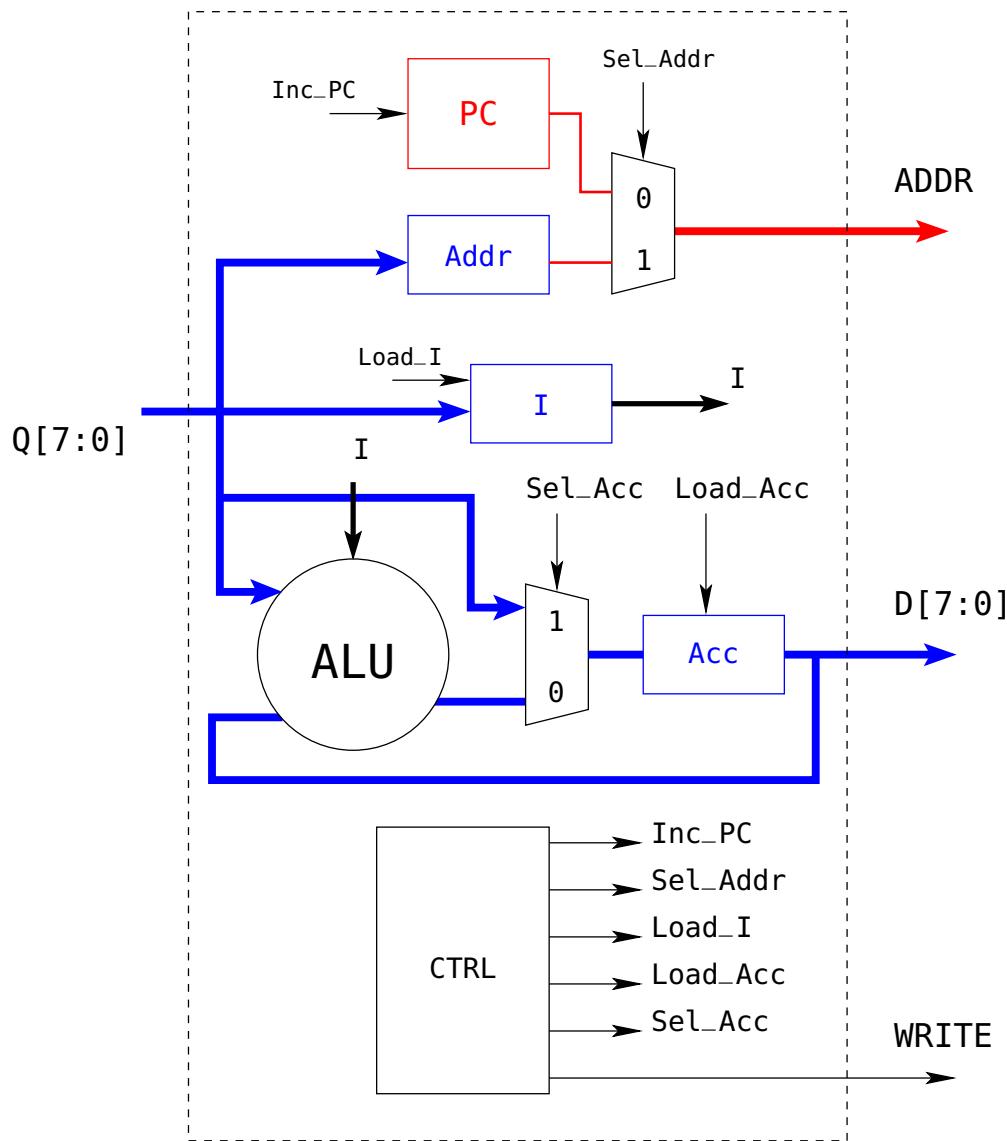

FIGURE 4.1: Une mémoire minimalist

La RAM possède trois bus :

- un bus d'adresses, **ADDR[7:0]** indiquant l'emplacement en mémoire de la donnée à laquelle on accède,

- un bus de données d'entrée, **D[7:0]**, pour les données qu'on va écrire en RAM,

- un bus de données de sortie, **Q[7:0]**, pour les données qu'on lit en RAM,

ainsi que

- un signal de contrôle sur 1 bit, **WRITE**, indiquant si on est en train de faire une *lecture* dans la RAM (**WRITE==0**), ou une *écriture* (**WRITE==1**).

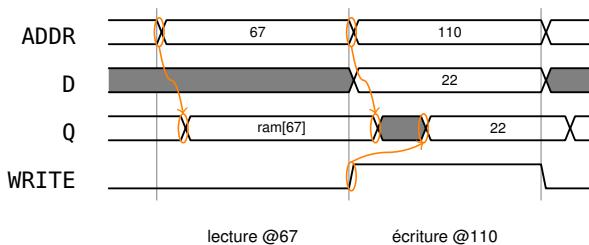

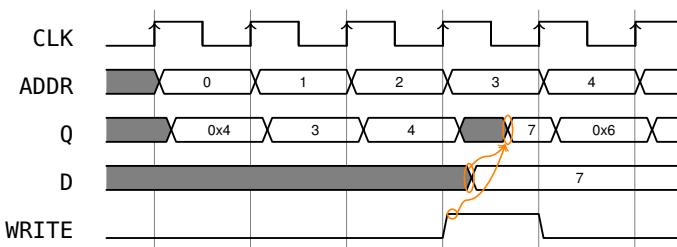

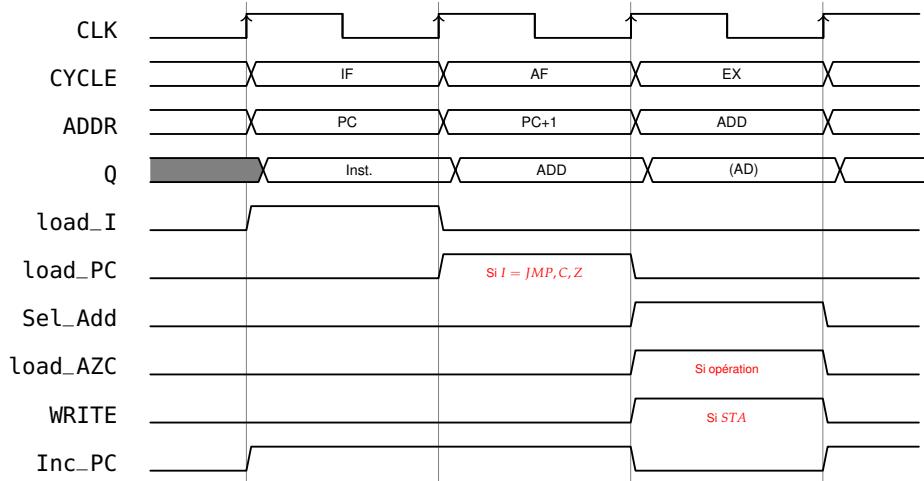

La figure 4.2 montre les chronogrammes d'une lecture et d'une écriture.

FIGURE 4.2: exemple d'accès à la RAM

Le fonctionnement de la RAM est le suivant :

- la RAM présente en permanence sur sa sortie **Q[]** la donnée stockée à l'adresse présente sur **ADDR[]**

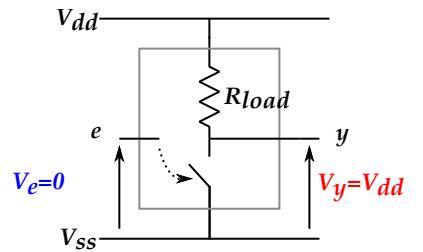

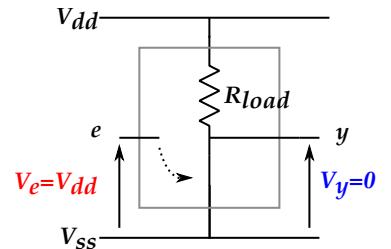

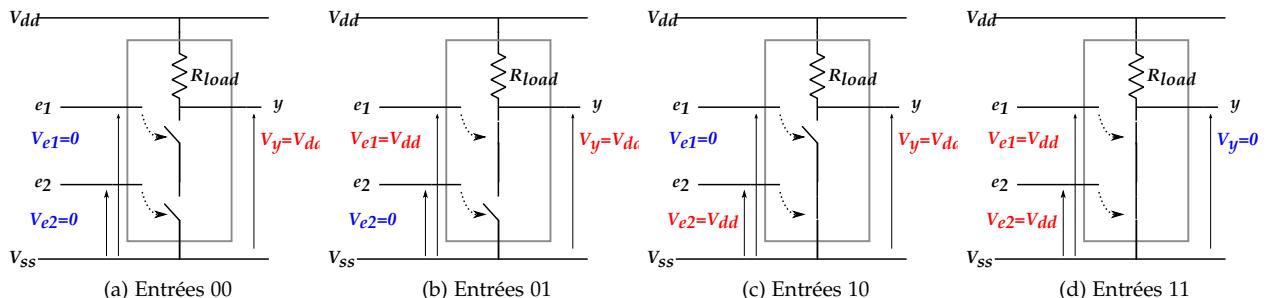

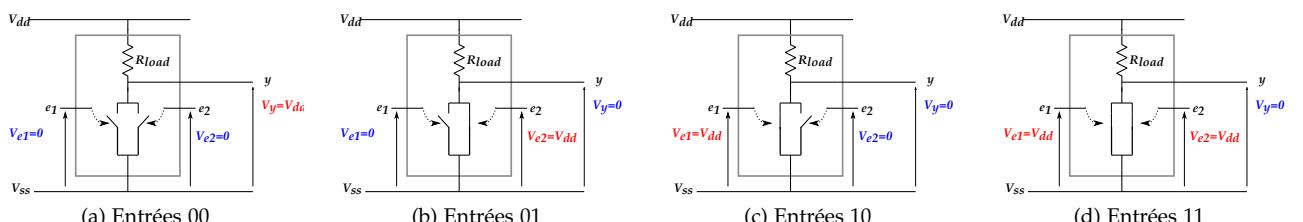

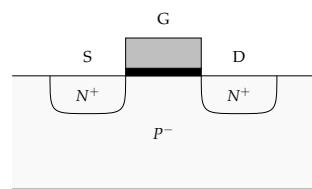

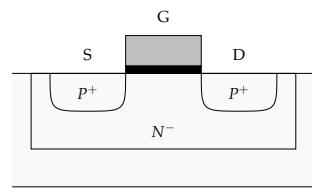

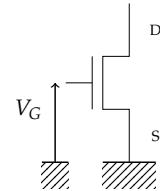

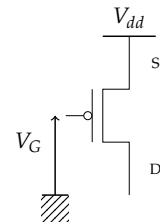

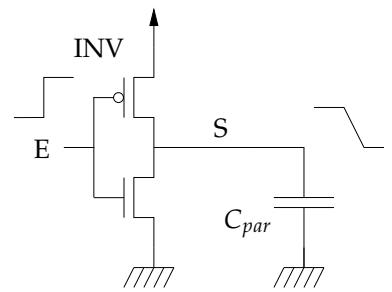

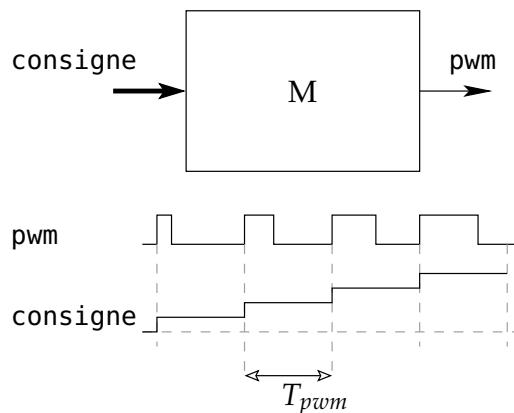

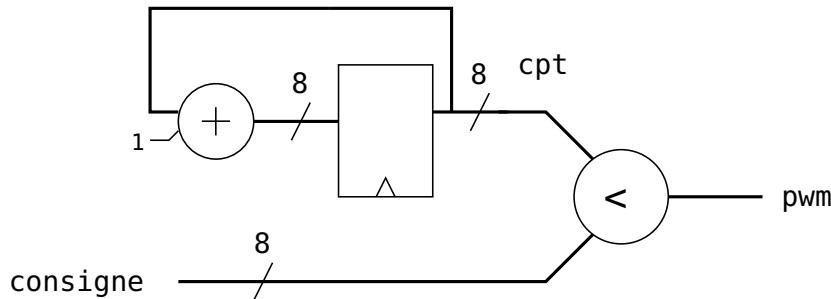

- si cette donnée n'est pas utile, on l'ignore,