# ELECINF102

## Processeurs et Architectures Numériques

Partie théorique

Jeudi 14 juin 2012

Sans calculatrice

Document autorisé : une feuille recto-verso

Durée: 45 minutes

Ce contrôle comporte trois parties **indépendantes** :

1. Questions de cours

2. Filtre

3. Compte à rebours

N'oubliez pas d'inscrire nom, prénom, et numéro de casier sur votre copie.

Bon courage !

## 1 Questions de cours

1. Donner la représentation en binaire de -5 sur 5 bits.

2. Sur  $N$  bits, quel est l'intervalle des nombres non signés représentable ?

3. Sur  $N$  bits, quel est l'intervalle des nombres signés représentable en CA2 ?

4. Donner la définition des temps  $t_{co}$ ,  $t_{hold}$  et  $t_{set-up}$  d'une bascule D.

## 2 Conception d'un filtre numérique

### 2.1 Additionneur

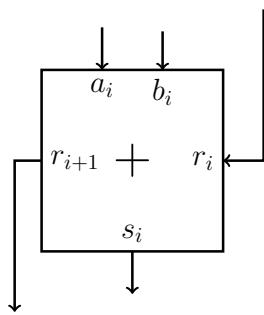

Soit l'additionneur unitaire suivant :

Dont les temps de propagation sont :

- $\delta s$  : des entrées  $a_i, b_i$  et  $r_i$  vers la sortie de somme  $s_i$ .

- $\delta r$  : des entrées  $a_i, b_i$  et  $r_i$  vers la sortie de retenue  $r_{i+1}$ .

Cet additionneur unitaire est utilisé pour construire un additionneur à propagation de retenue de deux nombres de 8 bits.

1. Donnez le schéma représentant la structure de cet additionneur.

2. Exprimez le temps de propagation de l'additionneur 8 bits en fonction des temps de propagation de l'additionneur unitaire.

### 2.2 Filtre

Nous voulons réaliser un filtre numérique sur des échantillons  $e_n$  qui arrivent les uns après les autres à la cadence de l'horloge d'acquisition  $clk$ . Chaque échantillon  $e_n$  est positif et est codé sur 8 bits

Le filtre à réaliser calcule à chaque période de l'horloge la moyenne des 8 derniers échantillons.

$$f_n = \frac{1}{8} \cdot \sum_{i=0}^7 e_{n-i}$$

### Calcul de la somme

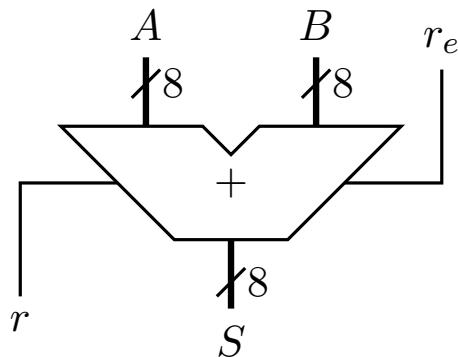

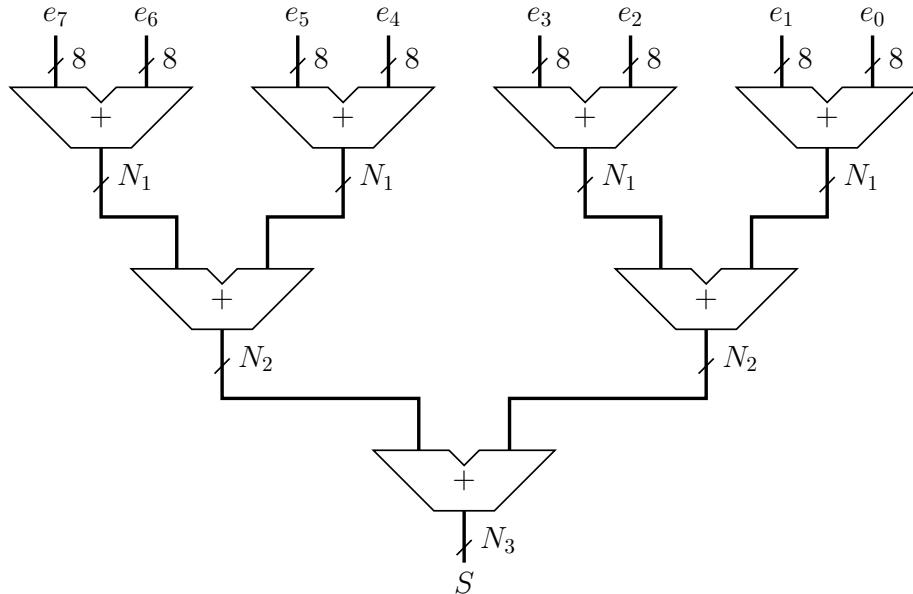

Nous voulons utiliser la structure en arbre suivante qui utilise des additionneurs à propagation de retenue.

- Précisez pour chaque niveau de cet arbre d'additionneurs le nombre de bits nécessaires  $N_1$ ,  $N_2$  et  $N_3$  pour ne pas avoir de dépassement.

- Proposez une solution pour présenter les huit derniers échantillons en même temps aux entrées de l'arbre d'additionneurs.

- Nous ajoutons un registre à la sortie de l'arbre d'additionneurs pour avoir une sortie synchrone. En négligeant les temps de propagation dans les registres, quelle est la fréquence maximale à laquelle les échantillons peuvent arriver ?

- Comment obtenir la partie entière et la partie fractionnaire de la moyenne des huit échantillons à partir de leur somme ?

### Question subsidiaire

- Proposez une structure (faites un schéma) permettant de faire le même calcul en utilisant moins de 3 additionneurs et/ou soustracteurs.

### 3 Compte à rebours

#### 3.1 Le système synchrone

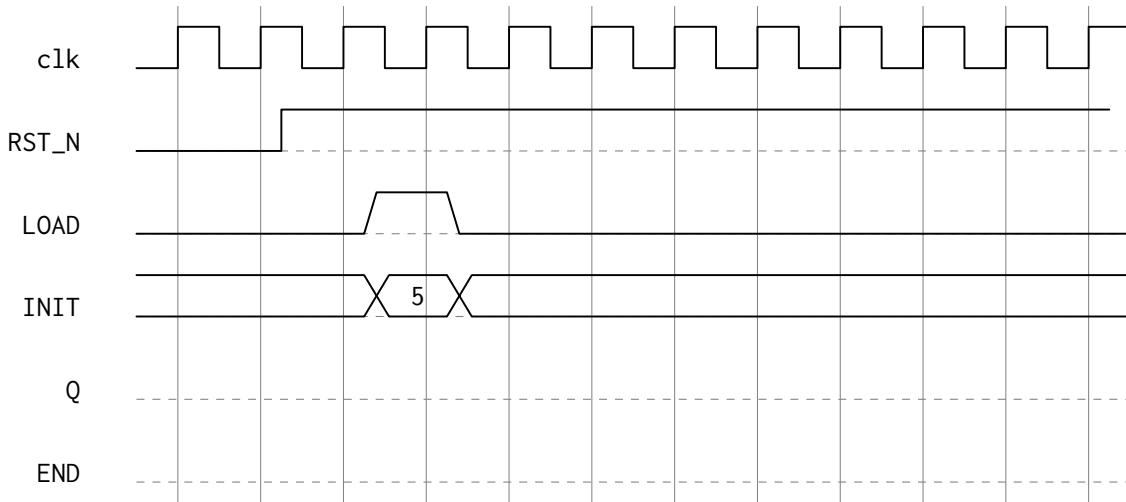

Nous voulons concevoir un système synchrone sur 4 bits permettant de réaliser un compte à rebours.

Les spécifications du système sont les suivantes :

- Un signal **RST\_N** force son état **Q** à zéro de façon *asynchrone*.

- Un signal **LOAD** permet de le charger l'état du système **Q** avec une valeur initiale de début du compte à rebours. Cette valeur est comprise entre 0 et 15 et vient de l'entrée **INIT** du système.

- Une fois arrivé à l'état zéro le système s'arrête et génère un signal **END** indiquant la fin.

1. Complétez le chronogramme suivant en respectant les spécifications ci-dessus.

2. Dessinez le schéma d'un opérateur permettant de savoir si un nombre A codé sur 4 bits est égal à zéro en utilisant des portes logiques de base.

Cet opérateur aura en entrée les 4 bits du nombre  $A = a_3, a_2, a_1, a_0$  et en sortie un bit  $Z$  tel que :

$$Z = \begin{cases} 1 & \text{si et seulement si } A == 0 \\ 0 & \text{si non} \end{cases}$$

3. Dessinez le schéma complet du système en utilisant l'opérateur précédent et des portes logiques combinatoires et séquentielles ainsi qu'éventuellement des opérateurs arithmétiques vus en cours.

4. On veut pouvoir relancer plusieurs fois le compte à rebours sans être obligé de le charger avec une nouvelle valeur. On ajoute le signal **RESTART** pour pouvoir re-déclencher le compte à rebours à partir de la *dernière valeur chargée* qui n'est donc plus forcément disponible sur l'entrée **INIT**.

Proposez une nouvelle architecture (re-faites un schéma) qui prend en compte cette nouvelle fonctionnalité.