## 1 Multiplieur-Accumulateur

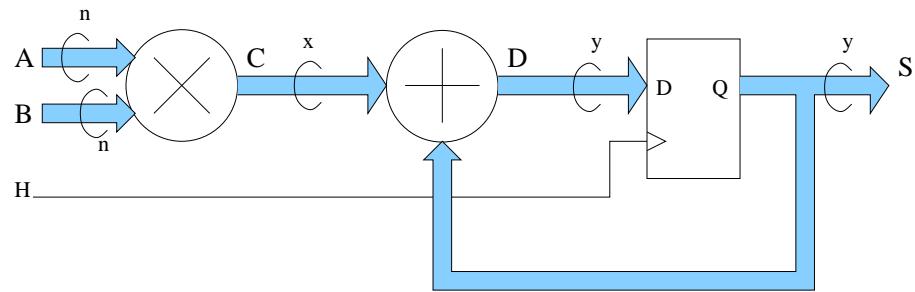

On voudrait concevoir un opérateur de traitement du signal de type MAC (Multiplieur-ACCumulateur). Deux nombres A et B signés (en complément à 2) sur  $n$  bits sont multipliés. Le résultat C sur  $x$  bits est additionné au registre sur  $y$  bits contenant un résultat intermédiaire. Chaque calcul se fait d'un façon synchrone, au rythme de l'horloge H. Le schéma de l'opérateur MAC est illustré dans la figure 1.

FIG. 1 : architecture du MAC.

NOTE : Les questions 1.X sont indépendantes

### 1.1 Etude de la représentation des nombres

- 1.1.1 Quelles sont les valeurs maximum et minimum que peuvent prendre A et B, nombres signés en complément à 2 sur  $n$  bits ?

- 1.1.2 Quelles sont les valeurs maximum et minimum du résultat de multiplication C ? En déduire le nombre bit  $x$  de C.

- 1.1.3 Si A et B ne prennent jamais la valeur minimum, quel peut être le nombre de bits  $x$  de C ?

- 1.1.4 Si l'accumulation se fait sur  $2^m$  nombres C, quel est le nombre de bits  $y$  du résultat S ?

### 1.2 Limiteur

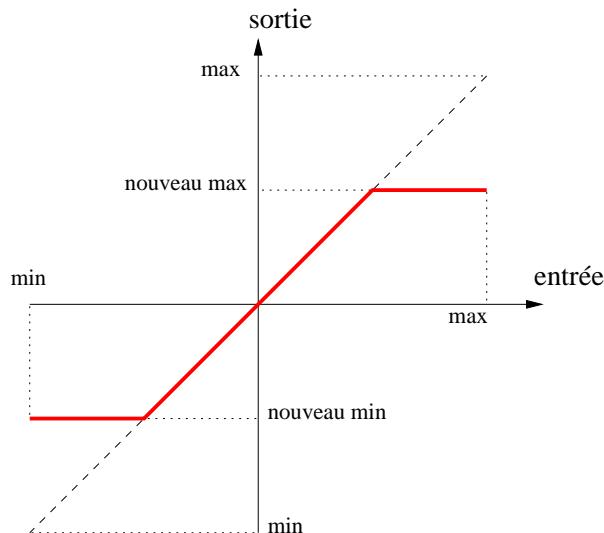

De façon à diminuer le nombre de bits, un circuit "limiteur" est inséré entre l'additionneur et le registre. la limitation ayant une entrée sur  $x$  bits et une sortie sur  $y$  bits ( $y < x$ ) peut se faire de 2 façons :

- soit on supprime les bits de faible poids, il s'agit alors d'une "troncature",

- soit on supprime les bits de fort poids. Dans ce cas il faut veiller à forcer en sortie la valeur minimum sur  $y$  bits si l'entrée est inférieure à cette valeur minimum. De même il faut forcer la valeur maximum sur  $y$  bits si l'entrée est supérieure à cette valeur maximum. Cette opération s'appelle la "saturation" ou "clipping". Elle est illustrée par la figure 2.

On considère un limiteur effectuant une fonction de saturation qui a pour entrée un mot C de  $x + 1$  bits et en sortie un mot D de  $x$  bits.

FIG. 2 : fonction de saturation.

- 1.2.1 Si  $C$  est un nombre binaire non signé, quelles sont les combinaisons de ses bits de poids fort permettant de tester simplement le dépassement des valeurs maximum et minimum en entrée ?

- 1.2.2 Même question si  $C$  est un nombre binaire signé en CA2. Dessinez-en alors le schéma de principe à base d'opérateurs fondamentaux (portes, bascules, additions, multiplexeurs,...).

### 1.3 Etude du chemin critique

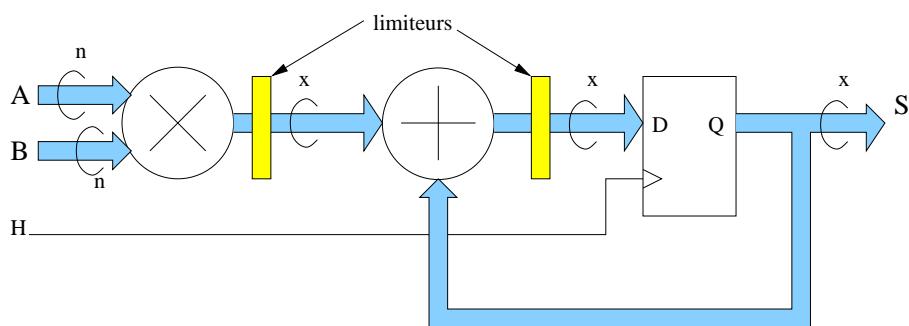

On considère que  $A$  et  $B$  sont issus de registres synchronisés avec  $H$ . Le schéma du MAC utilise maintenant des limiteurs sur  $x$  bits comme indiqué dans la figure 3

FIG. 3 : architecture du MAC.

Les temps de propagation des éléments sont donnés par le tableau 1 avec  $1ns$  comme unité de temps.

| REGISTRE | MULTIPLICATEUR | ADDITIONNEUR | LIMITEUR |

|----------|----------------|--------------|----------|

| 1        | $2n+1$         | $x$          | $x/2$    |

TAB. 1 : Temps de propagation

- 1.3.1 Quelle est la fréquence maximum de fonctionnement en fonction de  $n$  et  $x$  ?

- 1.3.2 Si un étage de pipeline est inséré juste après le limiteur en sortie de multiplicateur, quelle est l'expression de  $n$  par rapport à  $x$  permettant d'avoir un pipeline équilibré ?

#### 1.4 Contrôle du MAC

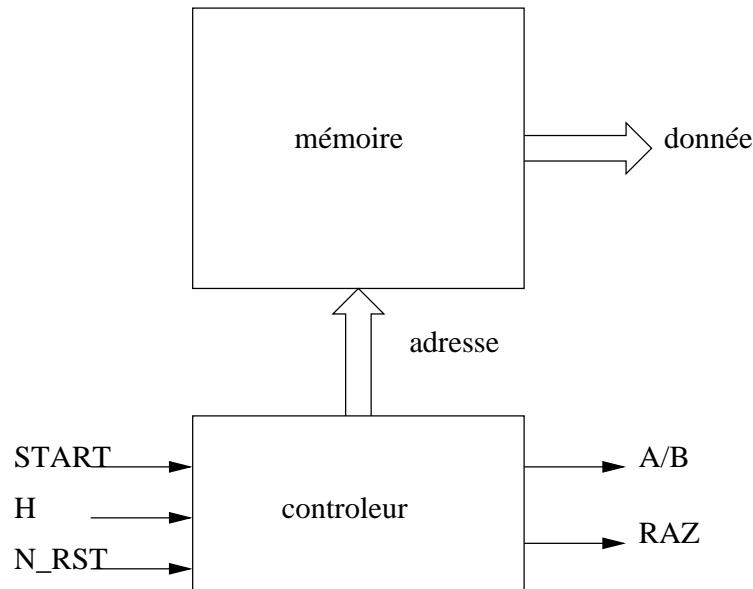

Le contrôleur est un circuit séquentiel synchrone avec l'horloge  $H$ . Il adresse une mémoire contenant les données A et B à multiplier puis à accumuler. Le bus d'adresses est sur  $m$  bits. La figure 4 illustre le schéma du contrôleur associé à la mémoire de données.

FIG. 4 : architecture du contrôleur et de la mémoire.

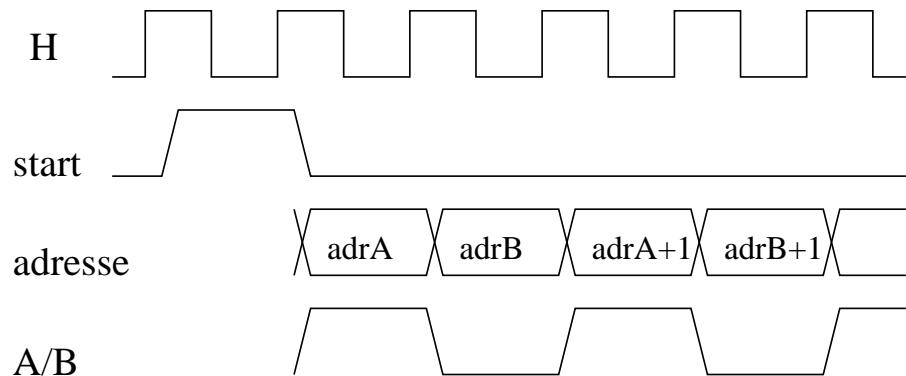

Le signal START indique qu'un nouveau traitement peut commencer. Les adresses de A et de B sont alors générées à tour de rôle par le contrôleur comme indiqué dans la figure 5. La zone mémoire des données A est espacée de  $\text{DELTA} = \text{adrA} - \text{adrB}$  de la zone mémoire des données B. Le signal A/B indique à quel nombre est associée l'adresse. Comme les données ne sont pas présentes simultanément, il manque un dispositif pour alimenter le MAC. Le signal RAZ est équivalent au signal START et permet de remettre à zéro l'accumulateur d'un façon synchrone.

FIG. 5 : chronogrammes du contrôleur.

- 1.4.1 Modifiez le MAC pour pouvoir mettre à zéro l'accumulateur d'une façon synchrone.

- 1.4.2 Modifiez le MAC pour pouvoir geler l'accumulateur quand le signal A/B est actif à 1.

- 1.4.3 Dessinez le schéma de principe du circuit en sortie de la mémoire de telle sorte que les signaux A et B soient séparés. Vous utiliserez les opérateurs fondamentaux (portes, bascules, additions, multiplexeurs,...) pour cela.

- 1.4.4 Dessinez le schéma de principe du contrôleur à base d'opérateurs fondamentaux.