## Performances de structures d'accumulation

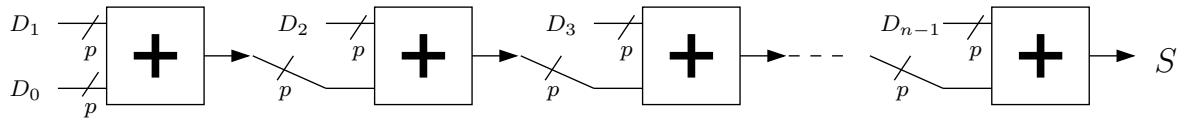

Nous désirons réaliser l'addition de  $n$  nombres  $D_i$  de  $p$  bits. Le résultat final restant codé sur  $p$  bits. Nous utilisons pour cela des additionneurs «1 bit» dont les caractéristiques temporelles sont les suivantes :

- Le temps de propagation de  $A, B, C_{in}$  vers la retenue sortante  $C_{out}$  est de 1 (dans une unité arbitraire).

- Le temps de propagation de  $A, B, C_{in}$  vers la somme  $S_{out}$  est de 1 (dans une unité arbitraire).

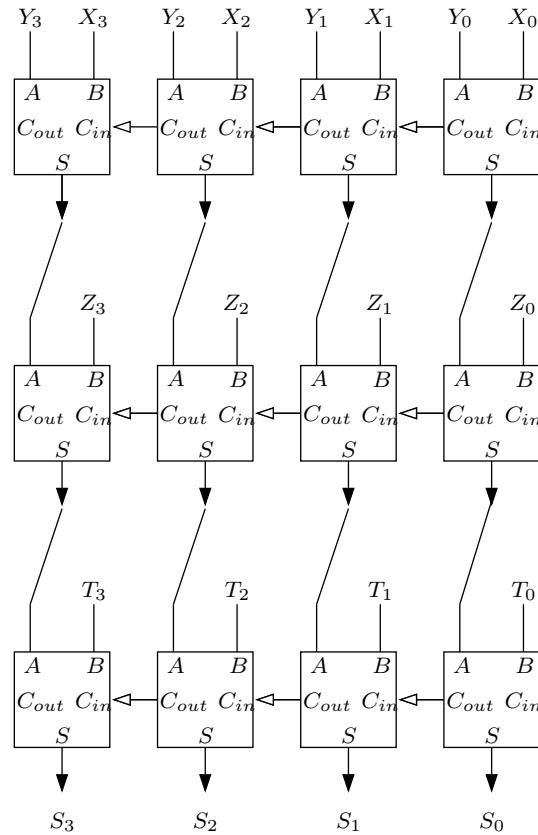

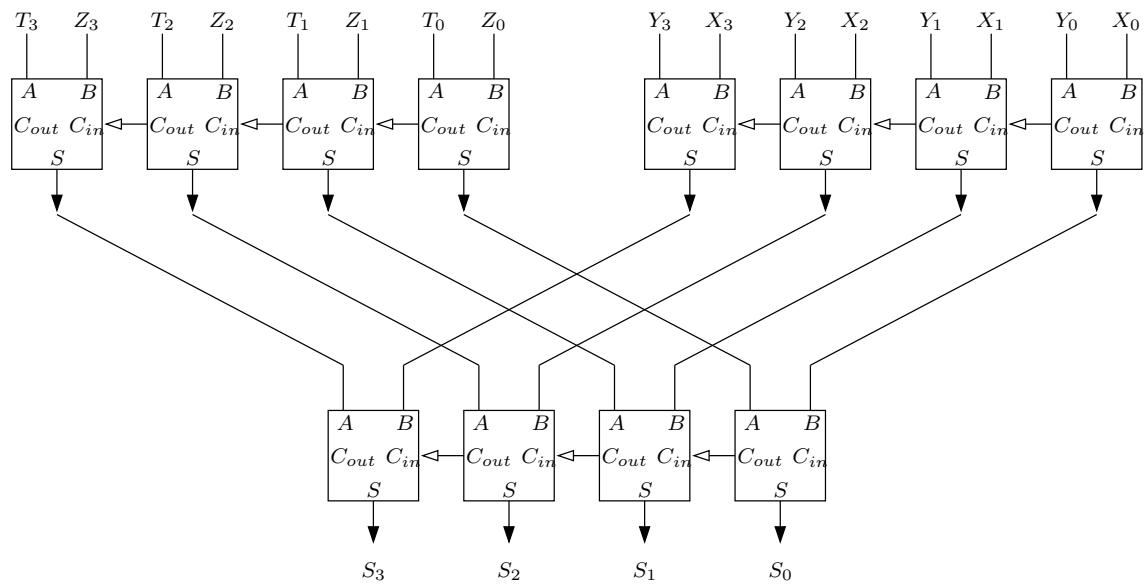

Les figures 3 et 4 présentent deux versions détaillées de l'addition de 4 mots de 4 bits  $X, Y, Z$  et  $T$ . Le résultat  $S$  étant codé sur 4 bits.

**Q1 : Complétez les figures 3 et 4 en indiquant le temps de calcul de chacun des signaux intermédiaires (sommes et retenues) ainsi que des sorties  $S_i$ , inclure la feuille de figures dans votre copie (avec votre nom)**

La figure 1 propose une version généralisée de la figure 3 permettant l'addition  $n$  mots de  $p$  bits. Elle utilise pour cela  $n-1$  additionneurs  $p$  bits.

FIG. 1 – Chaîne d'accumulation linéaire

**Q2 : Evaluatez le temps de propagation de la structure linéaire en fonction de  $n$  et  $p$**

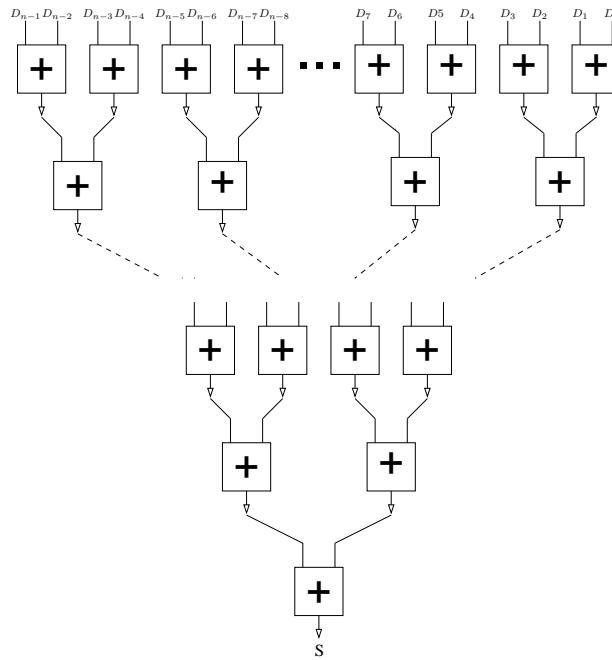

Nous généralisons maintenant la structure de la figure 4 à un arbre d'additionneurs  $p$  bits organisé selon la figure 2 .

**Q3 : Evaluatez le temps de propagation de la structure en arbre en fonction de  $n$  et  $p$ .** Pour faciliter la mise en équation, les valeurs de  $n$  pourront être limitées à des puissances de 2 ( $n = 2^q$ )

FIG. 2 – Chaîne d'accumulation en arbre

---

**Q4 : Quelle est la structure la plus efficace ? expliquez pourquoi..**

**Q5 : Dans un microprocesseur, ne disposant que d'un seul additionneur  $p$  bits nous ne pouvons effectuer qu'une seule addition par instruction. L'ordonnancement des calculs (linéaire ou en arbre) a t-il une influence sur le temps nécessaire pour faire l'accumulation. Expliquez**

Nom :

Prenom :

Casier :

FIG. 3 – Addition de 4 mots de 4bits : version 1

FIG. 4 – Addition de 4 mots de 4bits : version 2