1 ROL / ROR

Ces opérations sont combinatoires et seront donc implémentées dans l’ALU.

Remarque : comme le NOP, elles ne nécessitent pas d’opérande. De même, pour garder une cohérence (nous optimiserons ça plus tard), on garde un codage des instructions sur deux octets. Pour ROR et ROL, le deuxième octet n’a pas de signification...

2 Sortie BZ

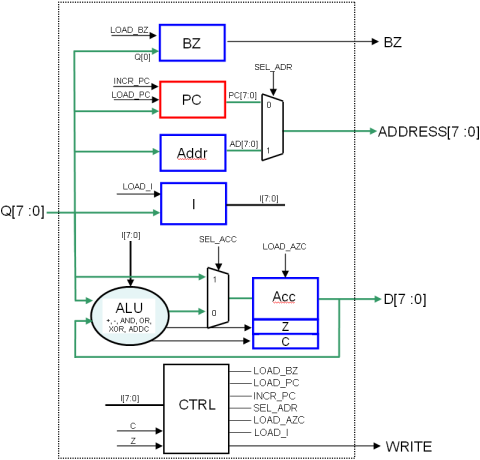

On ajoute un registre 1 bit, piloté par un signal d’enable appelé LOAD_BZ.

- l’entrée de ce registre est le bus de sortie de la RAM

- sa sortie est connectée à la broche de sortie buzzer du processeur...

LOAD_BZ sera généré par la machine à état, selon l’équation suivante : LOAD_BZ = (I[7:0] == OUT) et (état = EX)…

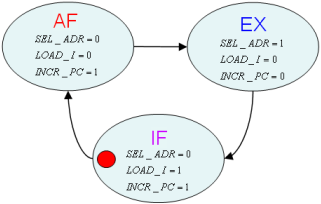

L’architecture globale est donc celle représentée sur la figure 1.13, avecun automate CTRL représenté figure 1.14.

Les équation sont laissées en exercice au lecteur !..

Remarque : le signal SEL_ACC ne sort pas de CTRL sur le schéma : il peut être inclus, avec le multiplexeur qu’il pilote, dans l’ALU...