Pour implémenter les sauts, il suffit de se donner la possibilité de remplacer le contenu de PC par la valeur lue en RAM.

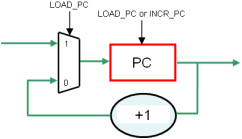

PC devient donc un peu plus complexe. C’est globalement un compteur, mais :

- il est incrémenté si son signal de commande INCR_PC = 1

- il est chargé avec une nouvelle valeur si un signal de chargement LOAD_PC = 1

- Enfin, si LOAD_PC et INCR_PC valent 1, LOAD_PC a la priorité...

Ceci peut être implémenté comme indiqué en la figure 1.10.

Pour simplifier les schémas, nous nommerons PC l'ensemble du bloc de la figure 1.10.

Il faut maintenant générer le signal LOAD_PC. Ce signal sera aussi généré par la machine à états CTRL. Le PC doit être remplacé lorsqu’on exécute un saut, et que le condition du saut est vérifiée. La nouvelle valeur est présente sur le bus de sortie de la RAM pendant le cycle 2.

On aura donc une équation du style :

(I[7:0] == JMP)

ou (I[7:0] == JNC et C == 0)

ou (I[7:0] == JNZ et Z == 0))

et (état = etat 2), alors 1,

sinon 0.

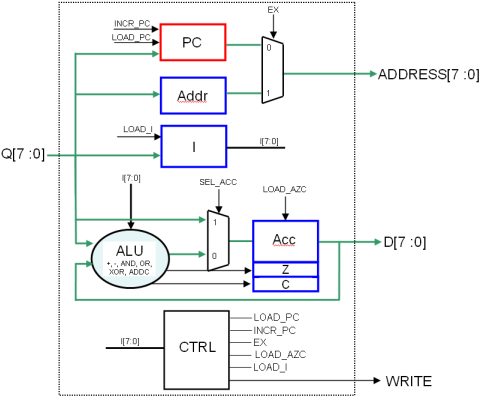

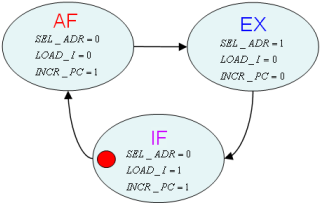

L’architecture globale est donc celle représentée sur la figure 1.11, avec un automate CTRL à peine modifié (même graphe d’état) représenté figure 1.12.

LOAD_ACC = (I[7:0] <> (STORE ou saut)) ET (Etat = Ex)

WRITE = (I[7:0] == STORE) ET (Etat = Ex)

LOAD_PC = si (I[7:0] == JMP ou I[7:0] == JNC et C == 0 ou I[7:0] == JNZ et Z == 0) et (état = Ad), alors 1, sinon 0