TP Machines à états

Objectifs

Au cours de ce TP, vous allez :

- Étudier un système de transmission utilisant des codes dits "À longueur variable" (ou "Variable Length")

- Concevoir une machine à état capable de décoder un tel code: VLD (Variable Length Decoder)

- Concevoir une machine à état capable de coder des nombres avec ce code: VLC (Variable Length Coder)

- Tester votre conception en grandeur réelle sur un FPGA,

- Améliorer votre décodeur (VLD) pour qu'il détecte certaines fautes...

Une introduction succincte aux codes à longueur variable

Les techniques courantes de transmission de données "compressées" font souvent appel aux codages "à longueur variable" (VLC pour Variable Length Coding). Ces codes utilisent les statistiques d'apparition des symboles du message pour attribuer aux symboles les plus fréquents des codes courts, et aux symboles plus rares des codes longs. Dans le cadre du TP, nous allons considérer un système de transmission dont les caratéristiques sont les suivantes :

- Les symboles font partie de l'ensemble: {1, 2, 3, 4, 5} et leurs fréquences statistiques sont:

- La probabilité d'apparition du symbole "1" est de 1/2,

- La probabilité d'apparition du symbole "2" est de 1/4,

- La probabilité d'apparition du symbole "3" est de 1/8,

- La probabilité d'apparition du symbole "4" est de 1/16,

- La probabilité d'apparition du symbole "5" est de 1/16.

Les codes VLC doivent être définis de manière à garantir un décodage sans ambigüité. Pour ce TP, nous utiliserons le codage suivant :

- Le symbole "1" aura pour code: "0",

- Le symbole "2" aura pour code: "10",

- Le symbole "3" aura pour code: "110",

- Le symbole "4" aura pour code: "1110",

- Le symbole "5" aura pour code: "1111".

Avec un codage de longueur fixe, il faudrait 3 bits par symbole pour transmettre ces données. Avec notre code à longueur variable vous pouvez aisément vérifier qu'il suffit "statistiquement" de 1,875 bits par symbole, d'où le gain en compression du flux de données.

Vous pourrez également vérifier que toute succession de bits est décodable en une succession de symboles.

Réalisation d'un décodeur

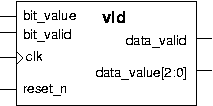

Nous désirons réaliser un bloc vld permettant de décoder les codes définis ci-dessus. Ce bloc est constitué d'une machine à états synchrone de Moore. Les caractéristiques de la transmission et les contraintes de traitement sont les suivantes :

-

Les symboles codés sont envoyés bit à bit par un signal bit_value, en commençant part les poids forts, de manière synchrone avec une horloge clk.

-

L'émetteur de symboles VLC signale au récepteur la présence d'un bit de symbole à transmettre par l'intermédiaire d'un signal bit_valid.

- L'émetteur de symboles VLC peut enchaîner les symboles sans interruption (pas de cycle d'attente).

-

L'émetteur de symboles peut interrompre temporairement la transmission (bit_valid=0) :

- entre les symboles, mais aussi

- au milieu de la transmission d'un symbole.

- Les symboles seront toujours intégralement transmis (l'émetteur ne fait pas d'erreurs).

-

Le décodeur génère un code data_value de 3bits correspondant au symbole décodé.

- Le signal data_value doit sortir exactement 1 cycle après l'arrivée du dernier bit du code VLC transmis.

-

Le décodeur signale la présence d'un symbole décodé par l'intermédiaire d'un signal data_valid qui ne doit rester à "1" que pendant 1 cycle de clk.

-

Le décodeur peut être initialisé par l'intermédiaire d'un signal reset_n asynchrone actif à l'état bas.

Les figures et tableaux suivants résument les interfaces du bloc VLD:

|

Nom |

Type |

Utilisation |

|

reset_n |

Entrée |

Initialisation de la machine à état, actif à l'état bas |

|

clk |

Entrée |

Horloge |

|

bit_value |

Entrée |

Bits de code qui entrent |

|

bit_valid |

Entrée |

Indique que le signal "bit_value" est valide |

|

data_value |

Sorties |

symbole décodé, recodé comme un entier sur 3 bits |

|

data_valid |

Sortie |

ne dure qu'un cycle, et indique que les sorties "data_value" portent un symbole décodé |

|

error |

Sortie |

Inutilisée pour le moment |

Travail à effectuer

-

Dessiner sur papier le schéma électrique de la machine à états, en séparant bien le registre qui mémorise l'état et les parties combinatoires, et en localisant où se connectent les entrées et les sorties,

-

Dessiner des chronogrammes de ce qui peut se passer dans différents cas, suivant les différentes valeurs possibles prises par les entrées,

-

Dessiner un graphe d'états de la machine à états vld, en précisant tous les états et toutes les transitions en fonction des valeurs des entrées,

-

Donner un nom court et clair à chaque état, indiquer la valeur des sorties data_valid et data_value pour chaque état, préciser l'état initial (celui du reset),

-

On nommera l'état courant EC et l'état futur EF, on définira la table de vérité de EF en fonction de EC et des entrées bit_valid et bit_value. On ne cherchera pas à donner une valeur binaire aux états (la compilation le fera automatiquement), la table de vérité contiendra directement les mnémoniques des états.

Exemple de début de table de vérité :

|

EC |

bit_valid |

bit_value |

EF |

|

DEBUT |

0 |

1 |

A1 |

|

A1 |

1 |

1 |

E2 |

|

... |

... |

... |

... |

- Déterminez le nombre minimum de bits nécessaires au codage des états.

-

Définir de même la table de vérité des sorties data_valid et data_value en fonction de EC :

|

EC |

data_valid |

data_value |

|

A1 |

1 |

1 |

|

E2 |

1 |

3 |

|

... |

... |

... |

-

Prenez la peine de lire la partie concernant le codage des machines à état en SystemVerilog, qui vous permettra :

- de déclarer les états de votre machine à états,

- de traduire très simplement vos tables de vérité.

-

Coder la machine à états en langage System Verilog. Pour cela, complétez le fichier vld.sv situé dans le sous-répertoire src (il est normalement déjà ouvert dans un onglet de l'éditeur eVim). Comme indiqué dans les commentaires du fichier, vous devez explicitement écrire 4 séquences de code :

- Le code qui déclare les noms des états pour les bus EC et EF,

- Le code séquentiel du registre qui mémorise l'état courant EC,

- Le code combinatoire du calcul de l'état futur EF,

- Le code combinatoire du calcul des sorties en fonction de EC.

-

Testez votre code en lançant la commande make simu_vld.

- Vérifiez vous-même le bon fonctionnement de votre décodeur et appelez votre encadrant pour qu'il constate le résultat.

Réalisation d'un codeur

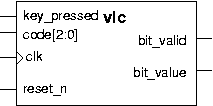

Le bloc vlc est le codeur qui génère les signaux transmis au décodeur que l'on vient de réaliser. Un opérateur humain dispose de 5 boutons numérotés de 1 à 5. Lorsque l'opérateur appuie sur un bouton, cela positionne en entrée de vlc le code du nombre entier de 1 à 5, en parallèle sur 3 fils nommés "code", et cela génère aussi une impulsion longue sur un fil nommé "key_pressed". Le codeur vlc sera réalisé sous forme d'une machine de Moore. Il doit transformer ses signaux d'entrées en signaux respectant le protocole VLC décrit précédemment, avec la donnée en sortie série sur un seul fil "bit_value".

Les figures et tableaux suivants résument les interfaces du bloc VLC :

|

Nom |

Type |

Utilisation |

|

clk |

Entrée |

Horloge |

|

reset_n |

Entrée |

Reset asynchrone, actif à l'état bas |

|

key_pressed |

Entrée |

Indique si une touche est appuyée. Ce signal reste actif au minimum une centaine de cycles |

|

code |

Entrée |

Code sur 3 bits de la touche appuyée. N'est valable que pendant que key_pressed est actif |

|

bit_valid |

Sortie |

indique que le bloc vlc génère sur "bit_value" un bit valide d'un code vlc |

|

vit_value |

Sortie |

valeur du bit de code vlc générée |

Les contraintes sont les suivantes :

-

vlc génère les séquences de bit dès que possible,

-

vlc ne génère qu'une seule séquence de bits lorsqu'une touche est appuyée (pas de répétition des symboles).

Travail à effectuer

-

Réaliser la machine vlc en suivant les mêmes étapes que pour vld, en tentant de minimiser le nombre d'états de la machine: dessin papier des chronogrammes puis du graphe d'état, écriture des tables de vérité des parties combinatoires, codage en langage système vérilog,

-

Éditez-le fichier vlc.sv en suivant les commentaires et le cadre déjà préparé,

-

Simulez votre codeur en exécutant la commande make simu_vlc.

-

-

Le test du couple (vlc,vld) se fait directement sur la maquette (make syn, make program). Vous utiliserez l'analyseur logique pour vérifier la bonne génération des signaux par vlc. Pour cela, les signaux suivants ont été reliés à l'analyseur logique:

clk

code (sur 3 entrées séparées)

key_pressed

bit_value

bit_valid

data_valid

data_value

-

L'analyseur logique sera synchronisé sur un front montant du signal key_pressed, de manière à saisir les enchaînements après l'appui sur un bouton.

-

Le signal key_pressed est relié au bouton KEY 3 de la maquette et le CODE est relié aux switch SW[2:0].

-

La valeur de data_value après passage dans vos codeur et décodeur est affichée sur l'afficheur sept segments HEX0.

Détection d'erreurs

Le code 5 est supprimé de l'ensemble des codes acceptables.

- Montrer que toutes les successions de bits ne sont plus acceptables comme étant la succession des codages de symboles. Le décodeur peut alors reconnaître qu'une succession de bits est erronée, et peut le signaler en sortie, en positionnant le signal "erreur". Vous allez modifier en ce sens votre décodeur.

- Modifier vld pour que :

- Il signale l'erreur au monde extérieur (via le signal "error", qui en outre doit rester à '1' jusqu'au prochain message)

- Il se resynchronise sur la prochaine séquence acceptable...

- Vérifiez le bon fonctionnement directement sur la maquette.