TP Logique séquentielle

Objectifs

Au cours de ce TP vous allez étudier et concevoir des fonctions de logique séquentielle : un compteur/décompteur et un système anti-rebonds. Les tâches à effectuer sont :

- Concevoir un compteur/décompteur : étudier la fonction, en effectuer la description en langage HDL, la simulation, la synthèse et le test sur la plate-forme (carte électronique contenant le FPGA).

- Étudier avec un analyseur logique les rebonds engendrés par les interrupteurs, qui peuvent entraîner des dysfonctionnements du compteur/décompteur.

- Concevoir un système anti-rebonds : étudier la fonction, en effectuer la description HDL, la simulation, la synthèse et le test sur la plate-forme.

Glossaire

- HDL : Hardware Description Language. Signifie que l'on décrit le schéma électronique en utilisant un langage de description de matériel tel que, par exemple, System Verilog.

- testbench : Banc de test du circuit en cours de conception. Pour vérifier que le circuit se comporte comme on le souhaite, on compare ses entrées/sorties à une référence. On a besoin d'une description des stimuli (entrées du circuit) et des réponses attendues (sorties du circuit), permettant de vérifier le bon comportement du circuit. Souvent le langage utilisé pour la description du testbench est identique à celui utilisé pour le circuit.

Architecture du compteur/décompteur

L'utilisateur dispose de deux boutons nommés A et B. On actionne le bouton A pour faire +1, et le bouton B pour faire -1. Vous allez concevoir le circuit compteur/décompteur (ou CD) qui doit être incrémenté lors de l'appui sur le bouton A et décrémenté lors de l'appui sur le bouton B. Lorsqu'on appuie sur un bouton, quelque soit la durée de cet appui, l'incrémentation ou la décrémentation ne se font qu'une seule fois. Autrement dit pour faire +3, il faut appuyer 3 fois sur le bouton A, en relâchant l'appui entre deux actions sur le bouton. Et ceci même si on appuie longtemps sur le bouton.

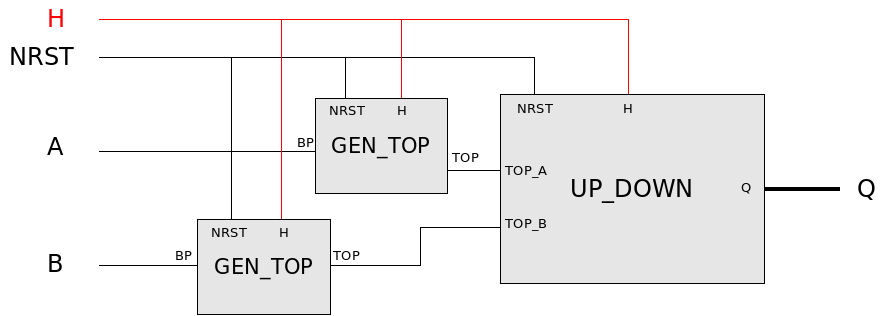

Le circuit à concevoir sera constitué de 3 blocs :

- 2 blocs GEN_TOP ayant pour but de délivrer respectivement 2 impulsions TOP_A et TOP_B dont la durée est de une seule période d'horloge pour chaque appui sur les boutons A ou B.

Dans la pratique, cet appui (qui peut aller d'une fraction de seconde à plusieurs secondes) dure beaucoup plus longtemps qu'une période d'horloge (qui peut se compter en micro-secondes ou nano-secondes). Le role de GEN_TOP est de générer un signal dont la durée (une période d'horloge) est indépendante de la durée de l'appui sur le bouton.

- Un bloc UP_DOWN qui reçoit les signaux TOP_A et TOP_B. Lorque TOP_A est reçu par ce bloc, le compteur interne est incrémenté, alors que TOP_B provoque la décrémentation. Lorsque les 2 TOPs sont reçus ensemble (en même temps), le fonctionnement n'est pas spécifié et donc le concepteur a le choix de l'opération (incrémentation ou décrémentation ou rien).

Les modules GEN_TOP et UP_DOWN, que vous allez concevoir, seront des circuits synchrones, actionnés par la même horloge H.

Le signal NRST sert à initialiser d'une façon asynchrone les registres des modules (Reset asynchrone).Il est actif à l'état bas.

La figure suivante illustre l'architecture du compteur/décompteur CD.

Conception et validation du compteur/décompteur

3.1 Conception du compteur-décompteur

- Faites tout d'abord un schéma sur le papier avec un crayon, pour concevoir le module GEN_TOP. Commencez par des chronogrammes, avec les signaux: l'horloge H, l'entrée BP (bouton-poussoir), la sortie TOP.

- Ensuite, trouver un schéma électrique qui permet de générer la sortie TOP, en choisissant les élements nécessaires (portes, bascules D) à la réalisation de GEN_TOP.

- Ensuite, traduisez votre schéma en instructions en langage SystemVerilog, en vous aidant de la partie décrivant la modélisation de la logique séquentielle en SystemVerilog. Ces instructions seront tapées en complétant le fichier gene_top.sv qui est déjà préparé. Faites attention à ne pas modifier les noms des signaux déjà définis (ils peuvent être différents de ceux de ces pages web).

- Faites de même pour la conception du module UP_DOWN: chronogramme, puis schéma, puis traduction en HDL. Prenez la peine de lire la partie décrivant les opérateurs arithmétiques en SystemVerilog. Complétez le fichier up_down.sv en respectant les noms des signaux déjà définis.

- Enfin terminez par le module CD (fichier cd.sv), en instanciant deux modules GEN_TOP et un module UP_DOWN.

3.2 Validation du compteur/décompteur (simulation logicielle)

Pour valider le fonctionnement du compteur et des générateurs de TOP nous avons mis à votre disposition un banc d'essai (testbench).

- Executez la commande make simu.

Le simulateur affiche un chronogramme des stimulis envoyés par le testbench ainsi que les réponses de votre circuit.

- Corrigez les éventuelles erreurs.

3.3 Programmation de la maquette (réalisation matérielle)

- Synthétisez votre modèle : make syn

- Programmez la maquette contenant le FPGA : make program

- Observez le fonctionnement réel de votre circuit électronique, en actionnant les deux boutons-poussoirs situés sur le petit circuit imprimé d'extension. Le circuit se comporte-t-il comme prévu?

Traitement des rebonds

Dans la réalité, aucun bouton poussoir ne fonctionne simplement comme on le souhaiterait: lorsqu'on appuie sur le bouton, la lame métallique qui bouge pour assurer le contact se met à vibrer et rebondir, si bien que pendant un certain temps, le circuit se ferme et s'ouvre plusieurs fois avant de se stabiliser. Vous avez remarqué que c'est le cas sur votre maquette. Le but de ce qui va suivre est de concevoir un système électronique qui remédie à ce problème.

4.1. Analyse des rebonds

- Tout d'abord, il faut analyser les types de défauts des boutons-poussoir (rebonds), en les observant sur les boutons réels, ceux de votre maquette. On a déjà connecté les sondes de l'analyseur pour visualiser le signal du bouton.

- L'analyseur logique est connecté sur les signaux suivants:

-

lclk

S0 pour le signal du bouton A

S1 pour le signal du bouton B

-

- Observez la forme des signaux.

- Déterminez la durée maximale des rebonds (en nombre de périodes de l'horloge lclk) sur les signaux S0 et S1

4.2. Conception d'un système "anti-rebonds"

L'idée générale d'un système anti-rebonds (ou "filtre anti-rebonds") est de ne pas accorder de signification aux changements rapides du signal pendant la durée qui correspond à celle des rebonds. C'est une stratégie possible car la durée de ces rebonds (quelques microsecondes) est très inférieure à la durée d'appui sur le bouton (de l'ordre de la seconde). Il n'y a donc pas de confusion possible entre les rebonds d'une part, et l'action manuelle de l'opérateur d'autre part. Pour pouvoir dire cela, il faut avoir une bonne connaissance de la durée maximale possible des rebonds, ce que vous venez d'observer et de mesurer.

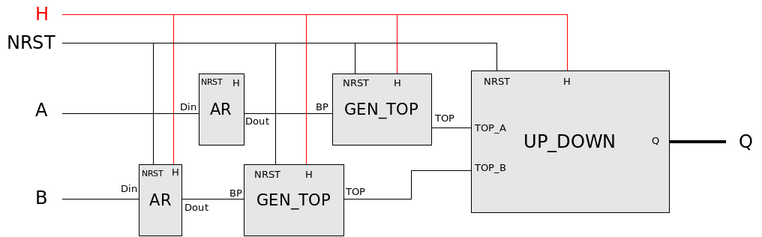

-

Imaginez un système anti-rebonds, basé sur un registre à décalage, permettant de filtrer les signaux d'entrée A et B. Ce système, nommé AR, sera intercalé sur les signaux des boutons, avant les GEN_TOP (voir figure suivante).

- Comme les fois précédentes, vous commencerez par des chronogrammes, puis vous ferez un schéma, puis vous traduirez ce schéma en HDL. Complétez le fichier anti_reb.sv.

- Adaptez le fichier cd.sv pour inclure les filtres anti-rebonds.

- Simulez le fonctionnement de l'ensemble en exécutant la commande make simu_rebonds. Avec cette commande, les signaux A et B du testbench vérifient le fonctionnement de votre AR. Corrigez d'éventuelles erreurs.

- Synthétisez l'ensemble (make syn) et reprogrammez la carte (make program).

- Vérifiez le fonctionnement réel de votre système, en actionnant manuellement les boutons. Vérifiez que vous filtrez correctement les rebonds.

L'usage d'un registre à décalage consomme beaucoup de bascules si la durée des rebonds est très grande devant la période d'horloge. On peut faire plus économique en bascules, qui sont des circuits comportant beaucoup de transistors.

- Imaginez un nouveau système anti-rebonds basé sur un compteur.

- Reprenez les étapes précédentes et vérifiez le bon fonctionnement.