Réalisation et validation d'une fonction combinatoire dans un circuit logique programmable

TP Logique combinatoire

Objectifs

Au cours de ce TP vous allez étudier le fonctionnement d'une unité arithmétique et logique (ALU: Arithmetic and Logic Unit). Cette unité purement combinatoire peut être utilisée dans un petit processeur.

Les tâches que vous devrez effectuer sont:

- Concevoir l'ALU: En se basant sur les acquis du cours vous allez concevoir une ALU modulaire à partir des opérations logiques de base.

- Valider l'ALU: Vous allez valider le fonctionnement de l'ALU en simulant de façon logicielle son fonctionnement puis en la mettant en oeuvre sur un "Circuit Logique Programmable" (CLP).

- Mesurer: Vous allez mesurer les temps de calcul de votre unité.

- Comprendre: Vous allez, à partir de votre ALU de base, concevoir des unités combinatoires plus complexes et étudier leurs performances en fonction des topologies choisies.

Environnement

2.1. Maquette

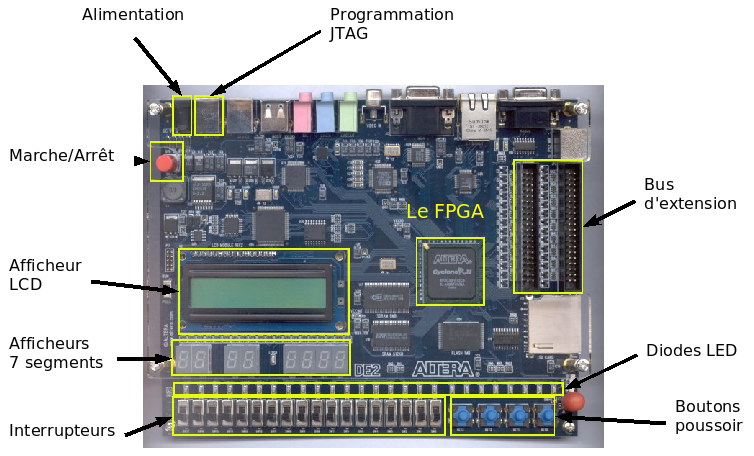

La maquette est construite autour d'un circuit logique programmable de type FPGA. Elle possède un grand nombre d'entrée/sorties toutes connectées au FPGA:

- 18 interrupteurs

- 4 Boutons poussoirs

- 8 afficheurs 7 segments

- 18 diodes LEDS rouges et 9 vertes

- 2 bus d'extension offrants 76 signaux accessibles

- 1 afficheur LCD 2 rangées de 16 caractères

- 1 entrée/sortie clavier/souris et RS232

- 2 ports USB

- 1 sortie moniteur VGA

- 1 entrée vidéo (NTSC/PAL/multi-format)

- Un codec Audio

Une photo de la maquette apparaît ci-dessous. Vous pouvez retrouver le FPGA, les E/S , le connecteur d'alimentation, le connecteur de programmation (via votre PC), ainsi que les connecteurs d'extension. Ces derniers permettront de connecter les sondes d'un analyseur logique de manière à observer les signaux sortants du FPGA.

En annexe, vous trouverez une documentation complète du FPGA et de la maquette.

2.2 Le logiciel de CAO

Les logiciels de CAO électronique aident le concepteur dans toutes les étapes du flot de conception d'un circuit. Les principales étapes pour un FPGA sont :

- La saisie : c'est l'écriture ou "codage" du fonctionnement du circuit et de sa décomposition en composants plus simples. On peut la considérer comme la traduction de la spécification. Elle peut être soit graphique avec des symboles de portes logiques , ou textuelle à l'aide de langages informatiques tels que "System Verilog", "verilog" ou "vhdl". Durant ce TP vous utiliserez le langage "System Verilog".

- La vérification : la vérfication consiste très souvent en une simulation du circuit, c'est à dire l'exécution d'un programme constitué d'un modèle du circuit dont les entrées sont pilotées par des variables évoluant temporellement. Le code saisi dans l'étape précédente sera le modèle utilisé par le "simulateur logique".

- La synthèse : cette étape est chargée de transformer et d'optimiser le modèle saisi en un ensemble de fonctions logiques disponibles dans le composant cible (notre FPGA). Cet ensemble de portes interconnectées s'appelle aussi "liste d'équipotentielles" ou "netlist"

- Le placement/routage : cette étape est chargée d'associer à chaque fonction logique de la netlist une ressource physique du FPGA. L'emplacement de ces ressources étant connu, les connexions entre portes sont transformées en vrais fils conducteurs entre ces ressources.

- La programmation : le fichier décrivant la "netlist" placée et routée est téléchargé dans le FPGA.

Spécifications de l'ALU

3. Spécifications de l'ALU

3.1. Généralités

- L'unité arithmétique et logique "ALU" d'un microprocesseur contient les opérateurs nécessaires au traitement des données. Les opérations peuvent être arithmétiques, logiques ou porter sur les bits (par ex. décalage d'un bit vers la gauche).

- Dans le cadre de ce TP:

- l'ALU de base reçoit deux nombres entiers non signés sur 4 bits : A[3..0] et B[3..0],

- Le type d'opération à effectuer est indiqué dans l'instruction en cours d'exécution, par l'intermédiaire d'un code d'opération CODE de 3bits.

3.2. Les entrées/sorties

- Le tableau suivant définit l'interface externe de l'ALU:

|

Nom |

Type |

Utilisation |

|

A[3:0] |

entrée |

Premier opérande de l'ALU. Entier non signé codé sur 4 bits |

|

B[3:0] |

entrée |

Deuxième opérande de l'ALU. Entier non signé codé sur 4 bits |

|

CODE[2:0] |

entrée |

Code déterminant l'opération à effectuer, sur 3 bits |

|

CIN |

entrée |

Retenue entrante, utilisée suivant l'opération demandée |

|

S[3:0] |

sortie |

Résultat sortant de l'ALU. Entier non signé codé sur 4 bits |

|

COUT |

sortie |

Eventuelle retenue sortante dont l'interprétation dépend de l'opération effectuée |

Remarques sur la notation vectorielle des données

- X[i:0] permet de représenter une donnée X codée sur (i+1) bits.

- X[i] est le bit de poids fort

- X[0] est le bit de poids faible

- X[j] est le bit de rang j (i >= j >= 0)

- X[k:l] est une tranche de (k-l+1) bits du vecteur X

3.3. Codage des opérations

Le tableau suivant représente les opérations à effectuer en fonction de CODE.

-

Attention : certains codes ne sont pas utilisés.

|

CODE |

Nom |

Équation |

Description |

|

000 |

AND |

A and B |

ET logique bit à bit |

|

001 |

OR |

A or B |

OU logique bit à bit |

|

010 |

XOR |

A xor B |

XOR logique bit à bit |

|

110 |

ADD |

A + B + CIN |

Addition sur 4 bits (avec propagation de retenue) |

|

111 |

SUB |

A - B - CIN |

Soustraction sur 4 bits (avec propagation de retenue) |

Travail à faire

L'addition de 2 mots de N bits peut être réalisée à partir de N cellules élémentaires d'addition sur 1bit.

Par analogie, l'ALU sera conçue de façon hiérarchique à partir d'une cellule élémentaire réalisant les opérations demandées sur 1bit. On mettra ensuite 4 exemplaires de cette cellule élémentaire côte à côte afin de réaliser l'ALU de 4 bits.

On commencera donc par la réalisation de la cellule élémentaire sur 1 bit.

4.1. La "cellule" 1 bit

- Le tableau suivant définit l'interface externe de la cellule 1 bit.

|

Nom |

Type |

Utilisation |

|

Ai |

entrée |

Premier opérande de la cellule. (sur 1bit) |

|

Bi |

entrée |

Deuxième opérande de la cellule. (sur 1bit) |

|

CODE[2:0] |

entrée |

Code déterminant l'opération à effectuer (sur 3 bits) |

|

CIN |

entrée |

Retenue entrante, utilisée ou non, suivant l'opération demandée |

|

Si |

sortie |

Résultat sortant de cellule. (sur 1bit) |

|

COUT |

sortie |

Eventuelle retenue sortante dont l'interprétation dépend de l'opération effectuée |

-

En vous aidant du cours sur les fonctions logiques de base et les opérateurs arithmétiques, définissez l'architecture de cette cellule. C'est un travail papier, vous pouvez à votre gré faire un shéma, définir des expressions algébriques ou des tables de vérité.

-

Prenez le temps de lire les deux premières partie de la page décrivant la syntaxe du SystemVerilog.

-

Enfin, décrivez en SystemVerilog la structure de votre cellule, en complétant le fichier cellule.sv qui est déjà ouvert dans la fenêtre de l'éditeur eVim. Respectez scrupuleusement les noms des signaux (majuscules-minuscules) et les indications. Vous écrirez séparément le code pour Si et le code pour COUT.

Nous avons préparé un environnement de vérification de votre cellule:

-

Sauvez votre fichier cellule.sv puis simulez votre cellule. Pour cela, exécutez la commande make sim_cell depuis la fenêtre de terminal déjà ouverte.

Si des erreurs sont signalées, vous devez corriger le fichier de code-source de votre cellule, puis relancer la simulation.

4.2. L'ALU 4bits

L'ALU 4 bits est obtenue en assemblant quatre cellules de base.

- Définissez l'organisation de cette structure

-

Complétez le fichier alu.sv

-

Vérifiez le bon comportement de votre ALU en utilisant la commande make sim_alu

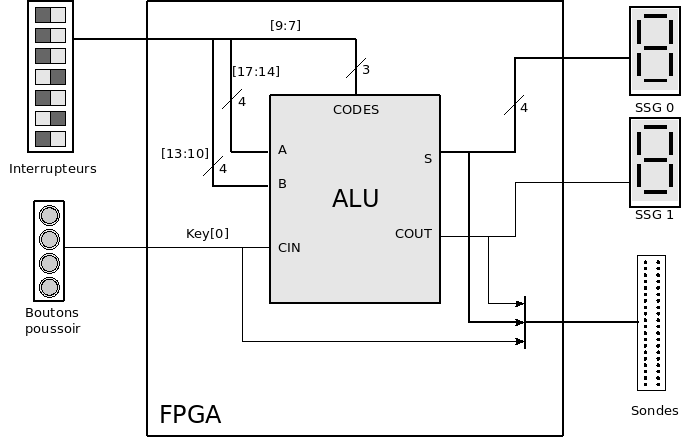

Pour le moment, nous n'avons fait que des simulations, il reste à intégrer réellement votre ALU dans la maquette. La figure suivante décrit l'interface simplifiée entre votre ALU et les éléments de la maquette. Cette interface existe et vous n'avez pas à la réaliser.

-

Executez la commande make syn_alu qui permet de réaliser la synthèse de l'ensemble du projet, et de générer la netlist pour la future programmation du FPGA.

Cette étape prend un certain temps de calcul pour s'exécuter, d'où l'intérêt de corriger les erreurs avant, en faisant des simulations. Le synthétiseur peut détecter des erreurs que la simulation n'a pas mises en évidence. Si tel est le cas, faites vous aider par votre encadrant pour en déterminer l'origine.

-

Avant de passer aux phases suivantes qui utuilisent le FPGA de la maquette ALTERA, vérifiez que la maquette est connectée, alimentée, et mise en marche (LEDs allumées).

-

Envoyez le programme au FPGA de la maquette, grâce à la commande make prg_alu.

Une fois le téléchargement effectué, vous pouvez tester le fonctionnement de votre ALU (électronique cette fois, non simplement simulé), en jouant sur les interrupteurs et les bouton-poussoirs. Le tableau suivant donne la correspondance des entrées/sorties sur la maquette:

|

Signal |

type |

correspondance |

type |

|

A |

entrée |

SW[17:14] |

interrupteurs |

|

B |

entrée |

SW[13:10] |

interrupteurs |

|

CODE |

entrée |

SW[9:7] |

interrupteurs |

|

CIN |

entrée |

Key[0] |

bouton poussoir |

|

S |

sortie |

Hex0 |

Aff. 7 segments |

|

COUT |

sortie |

Hex1 |

Aff. 7 segments |

- Montrez le résultat de votre travail à un encadrant du TP...

4.3 Temps de calcul d'un Additionneur 8bits

- A partir de l'ALU 4bits, déterminez la structure d'une ALU 8 bits

- Complétez le fichier alu_8bits.sv

- Simulez par la commande make sim_8bits.

Mesure des temps de propagation en mode addition

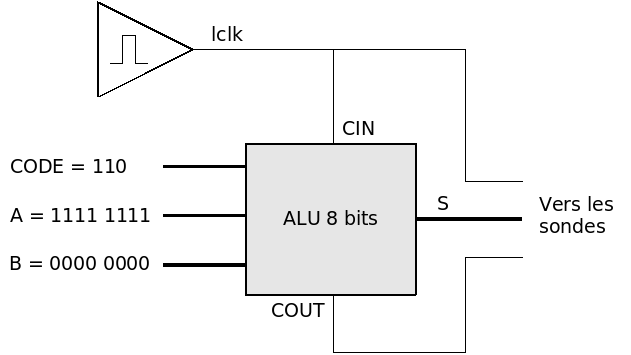

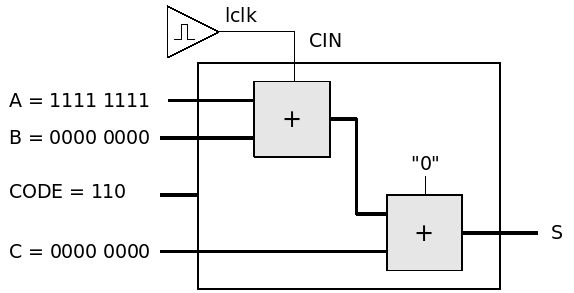

Pour mesurer les temps de calcul en mode additionneur de votre ALU 8bits, nous avons préparé une configuration où le code est forcé à la valeur correspondant à l'addition:

-

L'entrée A est forcée à 11111111

-

L'entrée B est forcée à 00000000

-

La retenue entrante CIN a été reliée à un signal d'horloge lclk qui prend à intervale régulier les valeurs 1 et 0.

-

4. Synthétisez l'alu 8 bits par la commande make syn_8bits

-

Programmez le FPGA par la commande make prg_8bits

- Quelle valeur doit prendre la sortie S lorsque Cin vaut 0 ?

- Quelle valeur doit prendre la sortie S lorsque Cin vaut 1 ?

Quand la retenue entrante passe de 0 à 1, le changement de S n'est pas instantané, c'est ce que vous devez observer. Pour cela nous avons connecté les sondes de l'analyseur logique. Les sorties suivantes sont visualisables:

-

lclk

S0 à S7 : les 8 sorties de l'ALU

Cout

- Configurez l'analyseur logique pour qu'il se synchronise sur un front du signal de la sonde correspondant à lclk. (faites vous aider pour cela par un encadrant)

- Observez les signaux, notez le temps de sortie de chacun des bits de S par rapport à l'arrivée de la retenue.

- Expliquez le comportement des sorties.

- Notez de même le temps de calcul total de l'addition.

4.4. Addition de 3 mots de 8bits

Nous désirons additionner 3 mots A,B et C codés sur 8bits. Le résultat attendu est codé sur 8 bits.

L'équation attendue est donc : S = A + B + C + Cin

- Déterminez la structure de calcul nécessaire en utilisant 2 instances de l'ALU 8bits du paragraphe 4.3

- Complétez le fichier alu_abc.sv

- Vérifiez votre structure par la commande make sim_abc

- Synthétisez vote alu par la commande make syn_abc

Nous allons déterminer la vitesse de calcul de votre structure en utilisant le shéma suivant:

-

AVANT DE PROGRAMMER votre alu, répondez au mini qcm suivant, et justifiez votre réponse (jouez le jeu SVP...)

- Je pense que le temps de calcul sera proche du temps de calcul de l'ALU 8bits.

- Je pense que le temps de calcul sera proche du double du temps de calcul de l'ALU 8bits

- Je n'ai aucune idée de la relation avec le temps de calcul de l'ALU 8bits

-

Programmez votre FPGA par la commande make prg_abc

- Examinez la sortie des signaux, et remettez éventuellement en cause la réponse précedente.

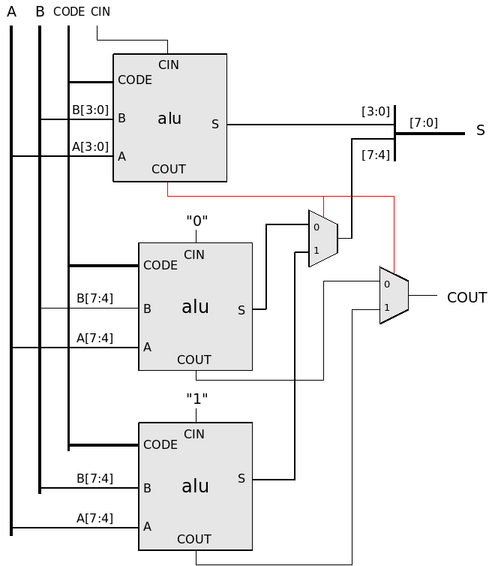

4.5 Un drôle d'additionneur 8 bits

Le shéma suivant représente une variante d'additionneur 8bits utilisant votre ALU 4 bits (celle du paragraphe 4.2)

- Complétez le fichier alu_csa.sv en reproduisant le montage proposé.

- Vérifiez votre ALU par la commande make sim_csa

- Synthétisez : make syn_csa

- Programmez : make prg_csa

- Examinez les sorties, déterminez le temps de calcul de l'addition 8bits et comparez au résultat du paragraphe 4.3

- Expliquez le résultat obtenu, et les avantages et inconvénients d'un tel montage.

Glossaire et annexes

Glossaire

- ALU : Unité Aritmétique et Logique (en français UAL).

- CLP : Circuit Logique Programmable : Circuit intégré numérique comportant un grand nombre de portes logiques dont les fonctions et les connections sont reprogrammables par téléchargement d'un fichier de configuration.

- FPGA : Field Programmable Gate Array : Famille de circuits logiques programmables, dont la programmation est "volatile": si vous coupez l'alimentation de votre carte, vous perdez la fonctionnalité stockée dans le FPGA...

- Analyseur Logique : Oscilloscope adapté à l'analyse de signaux logiques, qui possède un grand nombre de sondes de mesure, et interprète les signaux acquis comme des variables booléennes en fonction d'un seuil de tension.

- Netlist : (Liste de noeuds) fichier décrivant les portes utilisées et les interconnexions entre elles. Généré par les outils de synthèse et de placement, il décrit à un niveau bas la structure mise en oeuvre dans le circuit.

Annexes

- La carte Altera DE2.

- Le FPGA CycloneII