Chaque opération ne nécessite plus qu’un seul opérande :

- pour le load, c’est normal !

- pour le store, aucun opérande. Par contre, en RAM, à la suite de l’instruction store, il doit y avoir un emplacement libre pour stocker le contenu de l’accumulateur

- pour les opération à deux opérandes, l’un est en RAM, l’autre est interne à l’automate (c’est l’accumulateur)

Le contenu de la RAM se présentera donc maintenant ainsi :

| adresse | type du mot stocké | exemple | effet |

| 0 | instruction | load | |

| 1 | donnée | 3 | l’accumulateur contient maintenant 3 |

| 2 | instruction | + | |

| 3 | donnée | 4 | l’accumulateur contient maintenant 7 |

| 4 | instruction | - | |

| 5 | donnée | 1 | l’accumulateur contient maintenant 6 |

| 6 | instruction | store | |

| 7 | donnée | X | après l’exécution du programme cet emplacement en RAM contiendra “6” |

On remarque donc qu’une adresse sur deux contient une instruction, une sur deux contient une donnée (soit opérande, soit stockage du contenu de l’accumulateur)…

1 Les adresses

Comme précédemment, les adresses de la RAM sont parcourues de façon linéaire. On garde donc le compteur d’adresse incrémenté à chaque cycle d’horloge.

2 Les données

Pour effectuer les calculs, le processeur n’a plus besoin de connaître que deux informations : l’instruction et l’opérande. On garde donc le registre d’instruction (8 bits) qui stocke l’instruction à effectuer pendant qu’on va chercher l’opérande en RAM.

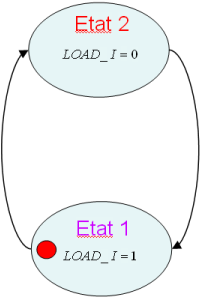

Par contre, auparavant on parcourait 4 emplacements en RAM pour chaque instructions, d’où une machine à états à 4 cycles. Maintenant on ne parcourt plus que 2 emplacements en RAM, donc une machine à état à 2 cycles devrait convenir…

A chaque instruction, le processeur effectuera ceci :

Pour une opération "normale" :

- aller chercher l’instruction en RAM, la stocker dans le registre d’instruction

- aller lire l’opérande en RAM, effectuer le calcul et stocker le résultat dans l’accumulateur (opération)

Pour un "load" :

- aller chercher l’instruction en RAM, la stocker dans le registre d’instruction

- aller lire l’opérande en RAM, et le stocker dans l’accumulateur (opération)

Pour un "store" :

- aller chercher l’instruction en RAM, la stocker dans le registre d’instruction

- écrire le contenu de l’accumulateur en RAM à l’adresse courante

Chaque instruction est donc traitée de façon très similaire :

- un cycle de récupération de l’instruction (dans lequel l’enable du registre d’instruction est mis à l’état haut).

- un cycle de traitement de l’instruction

3 L’accumulateur

Lors du second cycle, l’accumulateur peut subir trois traitements différents :

- pour une opération (+, −, AND, XOR, OR), l’accumulateur se voit modifié et chargé avec le résultat de l’opération

- pour un load, l’accumulateur est modifié aussi, et chargé avec la donnée sortant de la RAM

- pour un store par contre, l’accumulateur n’est pas modifié…

En entrée de l’accumulateur on mettra donc un multiplexeur qui présentera soit le résultat de l’opération en cours (si on exécute une opération standard), soit le contenu de la RAM (si on exécute un load). De plus, dans ces deux cas, le signal enable de l’accumulateur sera mis à l’état haut (pour autoriser sa modification) dans l’état 2 (quand on accède à la partie donnée de la RAM) Dans le cas d’un store, on laisse l’enable de l’accumulateur à l’état bas pour ne pas le modifier.

En d’autre termes, le signal de validation du chargement de l’accumulateur a pour équation en pseudo-langage :

LOAD_ACC = (Instruction <> STORE) ET (Etat = état 2)

Le pilotage du multiplexeur en entrée de l’accumulateur aura pour équation quelque chose du genre :

si (Instruction == LOAD) alors Q[7:0],

si (Instruction == opération) alors ALU(ACC, Q[7:0]),

si (Instruction == STORE) alors peu importe…)

Ce qui se simplifie en :

si (Instruction == LOAD) alors Q[7:0],

sinon ALU(ACC, Q[7:0]))

La sortie de l’accumulateur est branchée simultanément

- sur le bus d’entrée de la RAM (pour le cas d'une instruction "store")

- sur l’ALU (qui implémente, selon l’instruction à effectuer, l’addition, la soustraction, le XOR, etc…)

Enfin la génération du signal d’écriture en RAM est simple : il est mis à l’état haut quand l’instruction est un STORE, et qu’on est dans l’état 2. Le contenu de l’accumulateur est présenté sur l’entrée de la RAM (cf. ci dessus), l’adresse courante est sur le bus d’adresse de la RAM, la RAM est donc mise à jour avec la bonne valeur…

4 Bilan

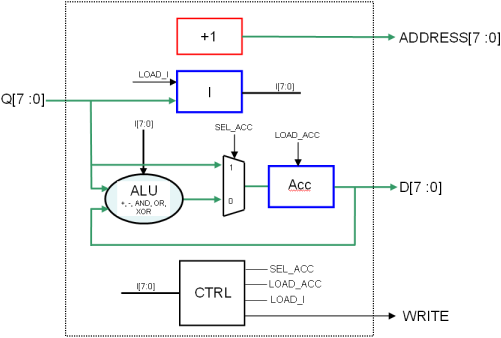

Nous disposons donc les éléments suivants :

- compteur d’adresse (PC)

- registre d’instruction

- accumulateur avec multiplexeur en entrée

- un automate générant les signaux LOAD_I, LOAD_ACC, WRITE et le contrôle du multiplexeur

Remarque : Les signaux générés par l'automate ne dépendent pas seulement de l’état courant de l'automate, mais aussi de la nature de l’instruction à exécuter. On nomme ce genre d'automate "machine de Mealy")

L’architecture globale est celle représentée sur la figure 1.6, et son graphe d’états en figure 1.7

avec :

LOAD_ACC = (I[7:0] <> STORE) ET (Etat = état 2)

WRITE = (I[7:0] == STORE) ET (Etat = état 2)

5 Performances

Pour une opération :

- version 1 : 4 cycles

- version 2 : 6 cycles (2 + 2 + 2)

Pour deux opérations chaînées :

- version 1: 8 cycles (4 + 4. Enfin, plus exactement, on ne savait pas faire…)

- version 2: 8 cycles (2 + 2 + 2 + 2)

Pour trois opérations chaînées :

- version 1 : 12 cycles (4 + 4 + 4. Même remarque)

- version 2 : 10 cycles

Bref, pour n opérations :

- version 1: 4n cycles

- version 2 : 2n+4 cycles si peut les enchaîner, 3n sinon.

On a donc tout intérêt à enchaîner les calculs. Ce qui est très souvent le cas en pratique…